Department of Electrical & Electronics Engineering

**Course File**

Subject: Power Electronic Subject Code: GR15A3018 Academic Year: 2018-19 Regulation: GR15 Year: III Semester: I

#### Department of Electrical & Electronics Engineering

#### **Course Title: <u>Power Electronics</u>**

#### Following documents are available in Course File.

| S.No. | Points                                                                          | Yes | No |

|-------|---------------------------------------------------------------------------------|-----|----|

| 1     | Institute and Department Vision and Mission Statements                          | J   |    |

| 2     | PEO & PO Mapping                                                                | 1   |    |

| 3     | Academic Calendar                                                               | 1   |    |

| 4     | Subject Allocation Sheet                                                        | J   |    |

| 5     | Class Time Table, Individual Timetable (Single Sheet)                           | J   |    |

| 6     | Syllabus Copy                                                                   | J   |    |

| 7     | Course Handout                                                                  | J   |    |

| 8     | CO-PO Mapping                                                                   | J   |    |

| 9     | CO-Cognitive Level Mapping                                                      | J   |    |

| 10    | Lecture Notes                                                                   | J   |    |

| 11    | Tutorial Sheets With Solution                                                   | J   |    |

| 12    | Soft Copy of Notes/Ppt/Slides                                                   | J   |    |

| 13    | Sessional Question Paper and Scheme of Evaluation                               | J   |    |

| 14    | Best, Average and Weak Answer Scripts for Each Sessional<br>Exam. (Photocopies) | J   |    |

| 15    | Assignment Questions and Solutions                                              | J   |    |

| 16    | Previous University Question Papers                                             | 1   |    |

| 17    | Result Analysis                                                                 | 1   |    |

| 18    | Feedback From Students                                                          | J   |    |

| 19    | Course Exit Survey                                                              | 1   |    |

| 20    | CO Attainment for All Mids.                                                     | J   |    |

| 21    | Remedial Action.                                                                |     | J  |

**Course Instructor / Course Coordinator**

**Course Instructor / Course Coordinator**

#### Karunakumar Davala

D karunakumar

(Name)

(Signature)

#### Department of Electrical & Electronics Engineering

#### Vision of the Institute

To be among the best of the institutions for engineers and technologists with attitudes, skills and knowledge and to become an epicenter of creative solutions.

#### **Mission of the Institute**

To achieve and impart quality education with an emphasis on practical skills and social relevance.

#### Vision of the Department

To impart technical knowledge and skills required to succeed in life, career and help society to achieve self sufficiency.

#### **Mission of the Department**

- To become an internationally leading department for higher learning.

- To build upon the culture and values of universal science and contemporary education.

- To be a center of research and education generating knowledge and technologies which lay groundwork in shaping the future in the fields of electrical and electronics engineering.

- To develop partnership with industrial, R&D and government agencies and actively participate in conferences, technical and community activities.

### **GOKARAJU RANGARAJU**

INSTITUTE OF ENGINEERING AND TECHNOLOGY

#### Department of Electrical & Electronics Engineering

#### **Programme Educational Objectives (B.Tech. – EEE)**

This programme is meant to prepare our students to professionally thrive and to lead. During their progression:

#### Graduates will be able to

- PEO 1: Have a successful technical or professional careers, including supportive and leadership roles on multidisciplinary teams.

- PEO 2: Acquire, use and develop skills as required for effective professional practices.

- PEO 3: Able to attain holistic education that is an essential prerequisite for being a responsible member of society.

- PEO 4: Engage in life-long learning, to remain abreast in their profession and be leaders in our technologically vibrant society.

#### **Programme Outcomes (B.Tech. – EEE)**

#### At the end of the Programme, a graduate will have the ability to

- PO 1: Apply knowledge of mathematics, science, and engineering.

- PO 2: Design and conduct experiments, as well as to analyze and interpret data.

- PO 3: Design a system, component, or process to meet desired needs within realistic constraints such as economic, environmental, social, political, ethical, health and safety, manufacturability, and sustainability.

- PO 4: Function on multi-disciplinary teams.

- PO 5: Identify, formulates, and solves engineering problems.

- PO 6: Understanding of professional and ethical responsibility.

- PO 7: Communicate effectively.

- PO 8: Broad education necessary to understand the impact of engineering solutions in a global, economic, environmental, and societal context.

- PO 9: Recognition of the need for, and an ability to engage in life-long learning.

- PO 10: Knowledge of contemporary issues.

- PO 11: Utilize experimental, statistical and computational methods and tools necessary for engineering practice.

- PO 12: Demonstrate an ability to design electrical and electronic circuits, power electronics, power systems; electrical machines analyze and interpret data and also an ability to design digital and analog systems and programming them.

| Programme Educational    | Programme Outcomes (POs) |   |   |   |   |   |   |   |   |    |    |    |

|--------------------------|--------------------------|---|---|---|---|---|---|---|---|----|----|----|

| <b>Objectives (PEOs)</b> | 1                        | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 |

| 1                        | Μ                        | М | - | - | Н | - | - | Η | Н | -  | Н  | Н  |

| 2                        | -                        | - | Μ | Μ | Н | Н | Н | - | - | -  | -  | Н  |

| 3                        | -                        | - | - | - | Η | Η | Μ | Μ | Μ | М  | Н  | Н  |

| 4                        | -                        | - | - | Μ | М | Н | Μ | Н | Н | -  | Μ  | Н  |

#### **PEOs & POs Mapping**

\* H: Strongly Correlating (3); M: Moderately Correlating (2)& L: Weakly Correlating (1)

HOD-EEE

#### Department of Electrical & Electronics Engineering

#### GRIET/DAA/1H/G/18-19

05 May 2018

#### ACADEMIC CALENDAR Academic Year 2018-19

#### III & IV B.TECH – FIRST SEMESTER

| S. No. | EVENT                                 | PERIOD                   | DURATION       |

|--------|---------------------------------------|--------------------------|----------------|

| 1      | 1 <sup>st</sup> Spell of Instructions | 02-07-2018 to 01-09-2018 | 9 Weeks        |

| 2      | 1 <sup>st</sup> Mid-term Examinations | 03-09-2018 to 05-09-2018 | 3 Days         |

| 3      | 2 <sup>nd</sup> Spell of Instructions | 06-09-2018 to 24-10-2018 | 7 Weeks        |

| 4      | 2 <sup>nd</sup> Mid-term Examinations | 25-10-2018 to 27-10-2018 | 3 Days         |

| 5      | Preparation                           | 29-10-2018 to 06-11-2018 | 1 Week3 Days   |

| 6      | End Semester Examinations (Theory/    | 08-11-2018 to 08-12-2018 | 4 Weeks 3 Days |

|        | Practicals) Regular/Supplementary     |                          |                |

| 7      | Commencement of Second Semester,      | 10-12-2018               |                |

|        | A.Y 2018-19                           |                          |                |

#### III&IV B.TECH – SECOND SEMESTER

| S. No. | EVENT                                 | PERIOD                   | DURATION       |

|--------|---------------------------------------|--------------------------|----------------|

| 1      | 1 <sup>st</sup> Spell of Instruction  | 10-12-2018 to 02-02-2019 | 8 Weeks        |

| 2      | 1 <sup>st</sup> Mid-term Examinations | 04-02-2019 to 06-02-2019 | 3 Days         |

| 3      | 2 <sup>nd</sup> Spell of Instruction  | 07-02-2019 to 06-04-2019 | 8 Weeks 3 Days |

| 4      | 2 <sup>nd</sup> Mid-term Examinations | 08-04-2019to 10-04-2019  | 3 Days         |

| 5      | Preparation                           | 11-04-2019 to 17-04-2019 | 1 Week         |

| 6      | End Semester Examinations(Theory/     | 18-04-2019 to 08-05-2019 | 3 Weeks        |

|        | Practicals) Regular                   |                          |                |

| 7      | Supplementary and Summer Vacation     | 09-05-2019 to 22-06-2019 | 6 Weeks 3 Days |

| 8      | Commencement of First Semester,       | 24-06-2019               |                |

|        | A.Y 2019-20                           |                          |                |

Copy to Director, Principal, Vice Principal, DOA, DOE, Balaji Kumar, DCGC, All HODs

(Dr. K. Anuradha) Dean of Academic Affairs

#### Department of Electrical & Electronics Engineering

| 2018-19 I sem Subject allocation sheet             |            |            |  |  |  |  |  |  |  |

|----------------------------------------------------|------------|------------|--|--|--|--|--|--|--|

| II YEAR( GR17)                                     | Section-A  | Section-B  |  |  |  |  |  |  |  |

| Special Functions and<br>Complex Variable          | Dr GS      | Dr GS      |  |  |  |  |  |  |  |

| Electromagnetic Fields                             | SN         | SN         |  |  |  |  |  |  |  |

| Network Theory                                     | MS         | MS         |  |  |  |  |  |  |  |

| DC Machines and<br>Transformers                    | Dr BPB     | Dr BPB     |  |  |  |  |  |  |  |

| Computer Organization                              | PRK        | PRK        |  |  |  |  |  |  |  |

| DC Machines Lab                                    | MP/DSR     | PRK/DSR    |  |  |  |  |  |  |  |

| Electrical Networks Lab                            | YSV/GBR    | YSV/GBR    |  |  |  |  |  |  |  |

| Electrical Simulation Lab                          | GSR/PS     | GSR/PS     |  |  |  |  |  |  |  |

| Environmental Science                              |            |            |  |  |  |  |  |  |  |

| III YEAR (GR15)                                    | Section-A  | Section-B  |  |  |  |  |  |  |  |

| Power Transmission System                          | VVRR/MP    | VVRR/MP    |  |  |  |  |  |  |  |

| Microcontrollers                                   | РК         | РК         |  |  |  |  |  |  |  |

| Power Electronics                                  | Dr TSK     | DKK        |  |  |  |  |  |  |  |

| Electrical Measurements&<br>Instrumentation (PE-1) | UVL        | UVL        |  |  |  |  |  |  |  |

| Solar & Wind Energy Systems<br>(OE-1)              | PSVD/Dr JP | PSVD/Dr JP |  |  |  |  |  |  |  |

| Sensors/Measurements&<br>Instrumentation Lab       | PSVD/PS    | UVL/PS     |  |  |  |  |  |  |  |

| Power Electronics Lab                              | PPK/MRE    | SN/MRE     |  |  |  |  |  |  |  |

| Microcontrollers Lab                               | RAK/DKK    | PK/DKK     |  |  |  |  |  |  |  |

| IV YEAR(GR15)                                      | Section-A  | Section-B  |  |  |  |  |  |  |  |

| Power Semiconductor Drives                         | YSV        | Dr DGP     |  |  |  |  |  |  |  |

| Power System Operation &<br>Control                | Dr JSD     | Dr JSD     |  |  |  |  |  |  |  |

| High Voltage DC Transmission<br>Systems            | MRE        | Dr SVJK    |  |  |  |  |  |  |  |

| Electrical Distribution Systems (PE-3)             | VVSM       |            |  |  |  |  |  |  |  |

| High Voltage Engineering (PE-<br>3)                | VUR        |            |  |  |  |  |  |  |  |

2018-10 I sem Subject allocation sheet

| Department                   |                | Electronics Enginee |

|------------------------------|----------------|---------------------|

| Soft Computing Techniques    | DAV            | DAK                 |

| (OE-3)                       | RAK            | RAK                 |

| DSP based Electrical Lab     | AVK/DKK        | AVK/DKK             |

| Power Systems Simulation Lab | VVSM / GSR     | VVSM / GSR          |

| Power Electronic Drives Lab  | MP/GBR         | MP/GBR              |

| I/I BEE(AICTE)               | A/B            | C/D/E               |

| BEE                          | ML             |                     |

| BEE                          | KS             |                     |

| BEE                          | МК             |                     |

| BEE                          | MVK            |                     |

| BEE                          | MNSR           |                     |

| Civil II/I (GR15)            | А              | В                   |

| ET                           | PPK            | РРК                 |

| M.Tech (PE)(AICTE)           | А              |                     |

| Electric Drives System       | Dr DGP         |                     |

| Power Electronic Converters  | Dr TSK         |                     |

| Power Quality                | AVK            |                     |

| Electric and Hybrid Vehicles | Dr BPB         |                     |

| Electrical Drives Laboratory | AVK/GBR        |                     |

| Power Electronics Lab        | SN/MS          |                     |

|                              |                |                     |

| M.Tech (PS)(AICTE)           | А              |                     |

| Power System Analysis        | Dr JSD         |                     |

| Power System Dynamics        | Dr SVJK        |                     |

| Power Quality                | AVK            |                     |

| Electric and Hybrid Vehicles | Dr BPB         |                     |

| Power System Steady State    |                |                     |

| Analysis Lab                 | VVSM/VVRR      |                     |

| Power System Dynamics Lab    | Dr<br>SVJK/YSV |                     |

#### Department of Electrical & Electronics Engineering

HoD-EEE

#### Department of Electrical & Electronics Engineering

#### GRIET/PRIN/06/G/01/18-19

BTech - EEE - B

| Wef                   |

|-----------------------|

| III year - I Semester |

| BTech - EEE - B III year - I Seme |                                                 |                       |                     |                                   |                                      |                                          |                                          |                                                    |                                      |                                 |

|-----------------------------------|-------------------------------------------------|-----------------------|---------------------|-----------------------------------|--------------------------------------|------------------------------------------|------------------------------------------|----------------------------------------------------|--------------------------------------|---------------------------------|

| DAY/ HOUR                         | 9:00 -<br>9:50                                  | 9:50 -<br>10:40       | 10:40<br>-<br>11:30 | 11:30 -<br>12:00                  | 12:00-<br>12:45                      | 12:45-<br>1:30                           | 1:30<br>-<br>2:15                        | 2:15<br>-3:00                                      | Roc                                  | om No                           |

| MONDAY                            | PE                                              | PE                    | MC                  |                                   | SMI Lab / PE Lab<br>B1/ B2           |                                          |                                          |                                                    | Theory                               | 4404                            |

| TUESDAY                           | PE                                              | PE                    | MC                  |                                   | MCLab / SMI Lab<br>B1/ B2            |                                          |                                          |                                                    | SMI Lab -<br>4507                    |                                 |

| WEDNESDAY                         | PE                                              | PE                    | PTS                 | BREAK                             | EMI SW                               |                                          | WE                                       | Lab                                                | MC Lab -<br>4505<br>PE Lab -<br>4405 |                                 |

| THURSDAY                          | PTS                                             | PTS                   | EMI                 |                                   | SV                                   | VE                                       | M                                        | IC                                                 |                                      |                                 |

| FRIDAY                            | PTS                                             | PTS                   | EMI                 |                                   | М                                    | IC                                       | SV                                       | VE                                                 | Class<br>Incharge:                   | M Lohita                        |

| SATURDAY                          | PTS                                             | EMI                   | EMI                 |                                   | PELab / MC Lab<br>B1/ B2             |                                          |                                          |                                                    |                                      |                                 |

| Subject Code                      | Su                                              | bject Nai             | me                  | Faculty<br>Code                   | Faculty name                         |                                          | Almanac                                  |                                                    |                                      |                                 |

| GR15A3016                         | Power Transmission<br>System                    |                       | VVRR/MP             | V Vijaya Rama<br>Raju/M Prashanth |                                      | 1 <sup>st</sup> Spell of<br>Instructions |                                          | 02-07-2018<br>to 01-09-<br>2018                    |                                      |                                 |

| GR15A2055                         | Mic                                             | crocontrol            | llers               | РК                                | P Prashanth                          |                                          | 1 <sup>st</sup> Mid-term<br>Examinations |                                                    | 03-09-2018<br>to 05-09-<br>2018      |                                 |

| GR15A3018                         | Powe                                            | er Electro            | onics               | DKK                               | D Karuna Kumar                       |                                          |                                          | 2 <sup>nd</sup> Spell of<br>Instructions           |                                      | 06-09-2018<br>to 24-10-<br>2018 |

| GR15A3017                         |                                                 | al Measur<br>nstrumen |                     | UVL                               | U Vijaya Lakshmi                     |                                          |                                          | 2 <sup>nd</sup> Mid-term<br>Examinations           |                                      | 25-10-2018<br>to 27-10-<br>2018 |

| GR15A3152                         | Solar & Wind Energy<br>Systems                  |                       |                     | PSVD/Dr<br>JP                     | P Sri Vidya Devi/Dr J<br>Praveen     |                                          | /i/Dr J                                  | r J Preparation                                    |                                      | 29-10-2018<br>to 06-11-<br>2018 |

| GR15A3019                         | Sensors/Measurements<br>and Instrumentation Lab |                       | UVL/PS              | U Vijaya Lakshmi/ P<br>Sirisha    |                                      | nmi/ P                                   | mi/ P End Semes<br>Examination           |                                                    | 08-11-2018                           |                                 |

| GR15A3020                         | Power Electronics Lab                           |                       |                     | SN/MRE                            | Syed Sarfaraz Nawaz/<br>M Rekha      |                                          |                                          | (Theory/<br>Practicals) Regular<br>/ Supplementary |                                      | to 08-12-<br>2018               |

| GR15A2059                         | Micro                                           | ocontrolle            | rs Lab              | PK/DKK                            | P Prashanth Kumar/ D<br>Karuna Kumar |                                          |                                          | Comm<br>Second                                     | 10-12-2018                           |                                 |

| HOD                               |                                                 |                       |                     |                                   | Со                                   | -ordinat                                 | or                                       |                                                    |                                      | DAA                             |

#### Department of Electrical & Electronics Engineering

|     | Work Load / D Karuna Kumar |             |              |                 |             |             |             |             |  |  |  |

|-----|----------------------------|-------------|--------------|-----------------|-------------|-------------|-------------|-------------|--|--|--|

|     | 9.00 PM                    | 10.00<br>PM | 11. 00<br>PM | 12.<br>00<br>PM | 1. 00<br>PM | 2. 00<br>PM | 3. 00<br>PM | 4. 00<br>PM |  |  |  |

| MON | Pow                        | er Elect    | ronic        |                 |             |             |             |             |  |  |  |

| TUE | Pow                        | er Elect    | ronic        |                 |             |             |             |             |  |  |  |

| WED | Pow                        | er Elect    | ronic        |                 |             |             |             |             |  |  |  |

| THU |                            |             |              |                 |             |             |             |             |  |  |  |

| FRI |                            |             |              |                 |             |             |             |             |  |  |  |

| SAT |                            |             |              |                 |             |             |             |             |  |  |  |

#### Department of Electrical & Electronics Engineering Syllabus Subject— Power Electronics Course Code: GR15A3018

B.Tech III Year I Sem

L:3T:1 P:0 C:4

#### UNIT-I

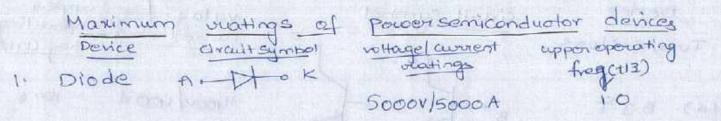

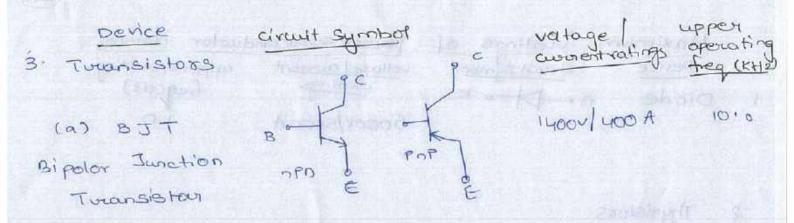

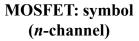

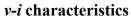

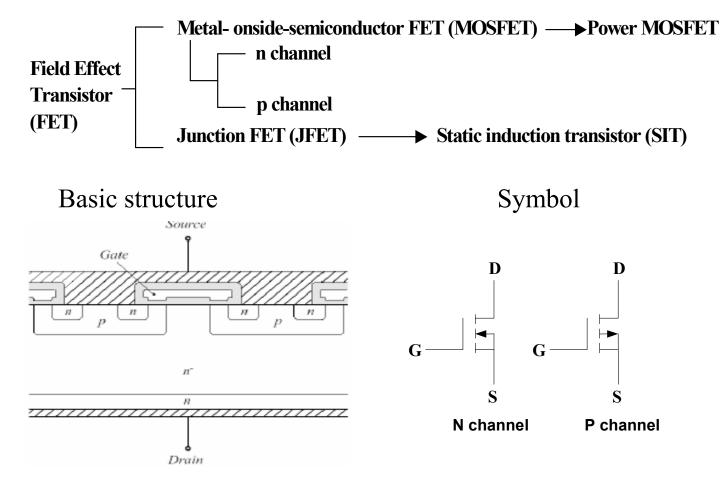

Power Semiconductor Devices: Thyristors Silicon Controlled Rectifiers (SCR's) BJTPower MOSFET and Power IGBT and their characteristics and other thyristors Basic theory of operation of SCR Static characteristics Turn on and Turn off methods-Dynamic characteristics of SCR Turn on and Turn off times-Salient points.

Two transistor analogy of SCR R,RC,UJT firing circuits Series and parallel connections of SCR's Snubber circuit details Specifications and Ratings of SCR's, BJT, IGBT - Numerical problems Line Commutation and Forced Commutation circuits.

#### UNIT-II

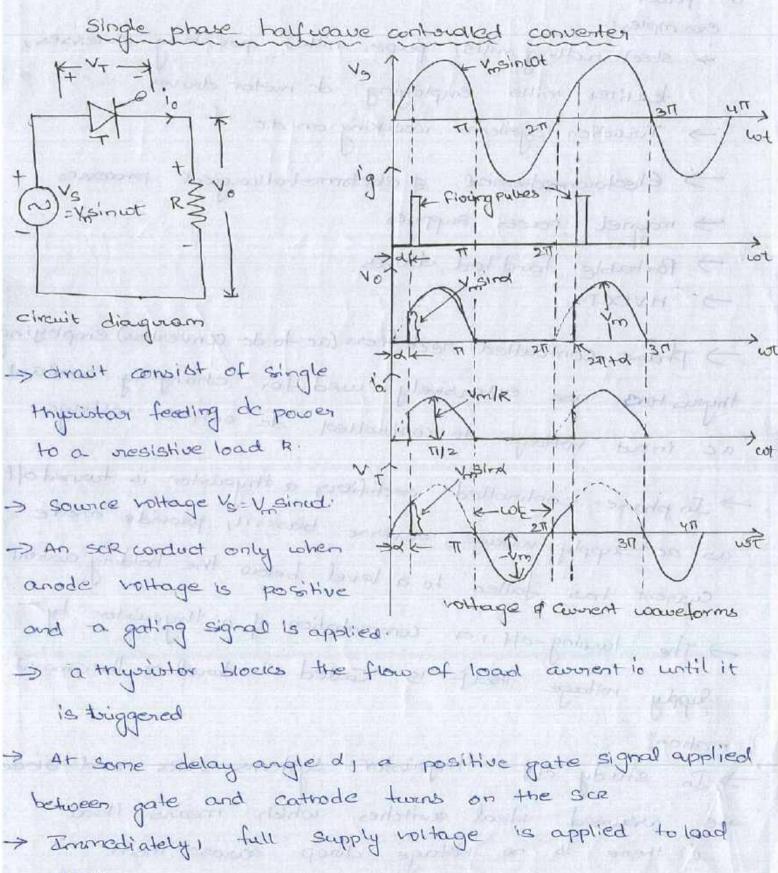

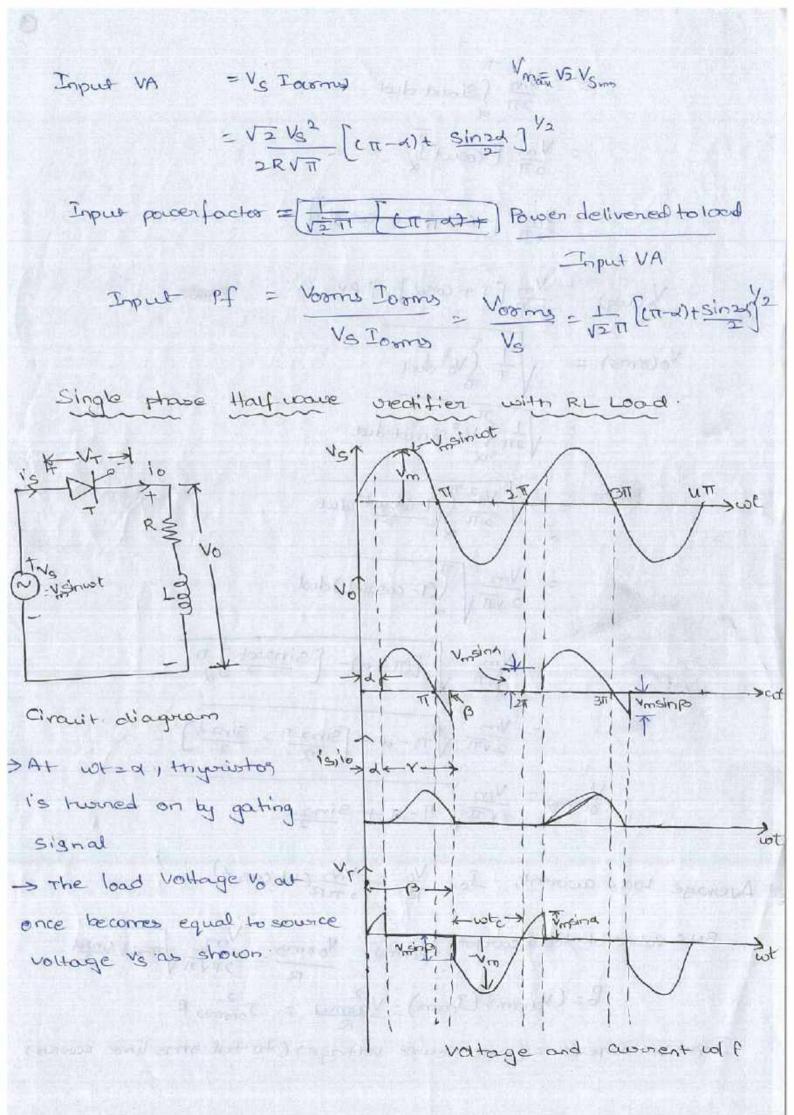

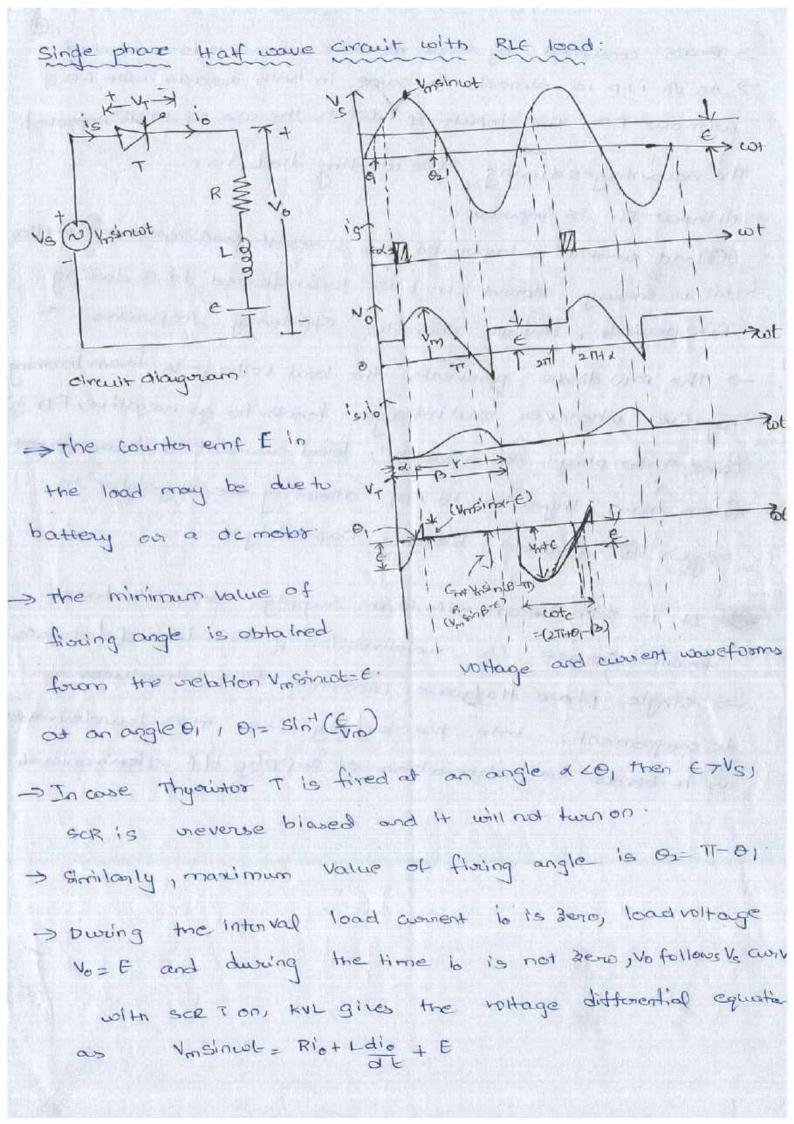

**Single Phase Half Wave Controlled Converters:** Phase control technique, Single phase Line commutated converters, Mid point and Bridge connections– Half wave controlled converters with Resistive, RL load and RLE load Derivation of average load voltage and current Active and Reactive power inputs to the converters without and with Freewheeling Diode Numerical problems

**Single Phase Fully Controlled Converters:** Fully controlledconverters, Midpoint and Bridge connections with Resistive, RL loads and RLE load Derivation of average load voltage and current Line commutated inverters, semi-converters, active and Reactive power inputs to the converters, Effect of source inductance Expressions of load voltage and current, Dualconverters Numerical problems.

#### UNIT-III

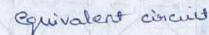

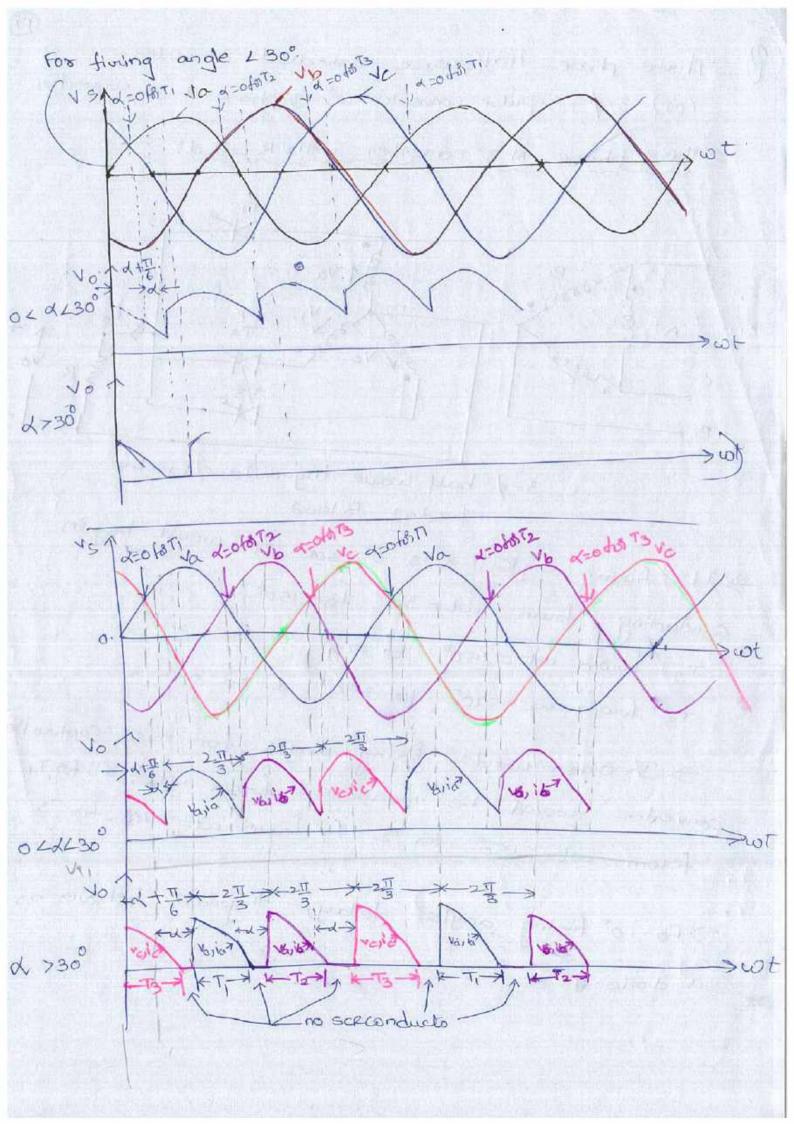

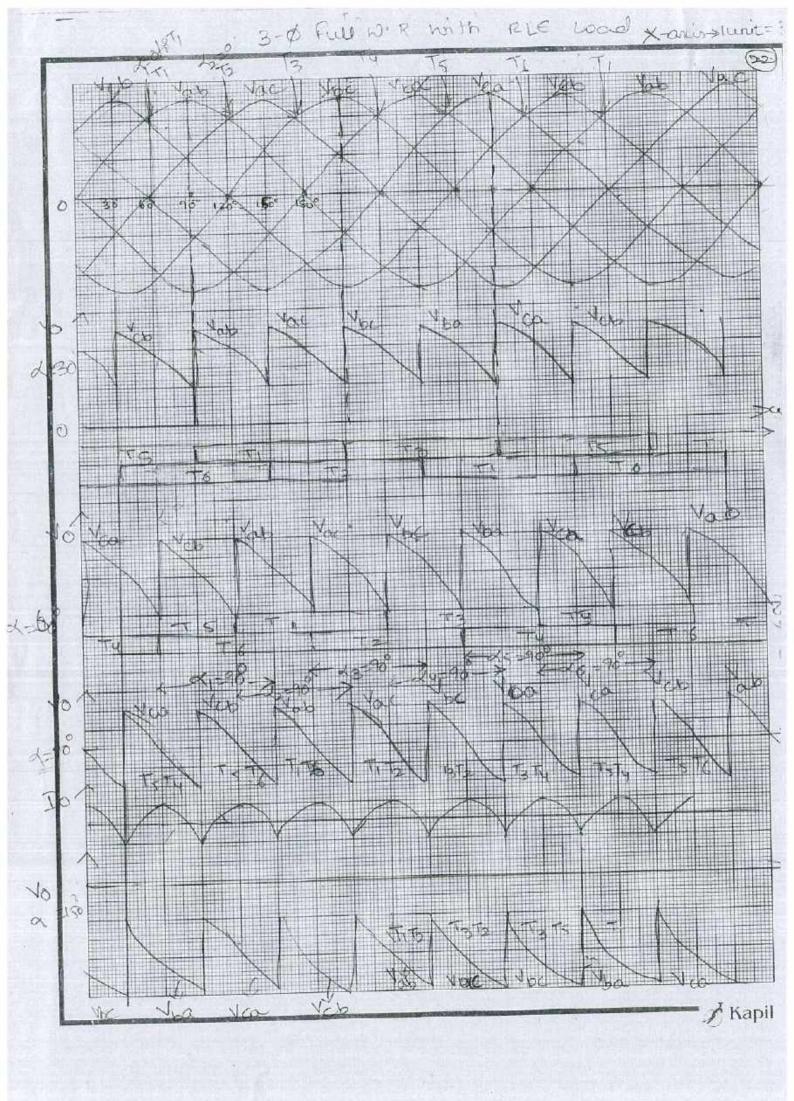

**Three phase converters:** Three pulse and six pulse converters Mid-Point and bridge connections average load voltage with R, RL load voltage and current with R and RL load and Semi converter Effect of Source inductance Waveforms Numerical Problems.

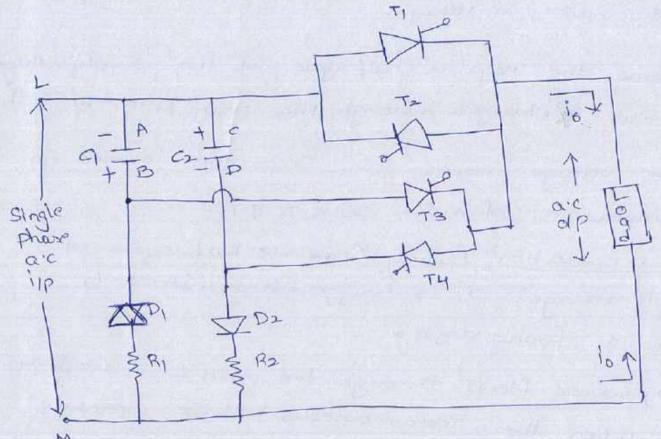

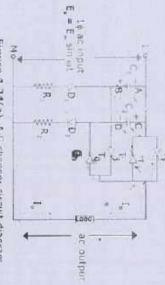

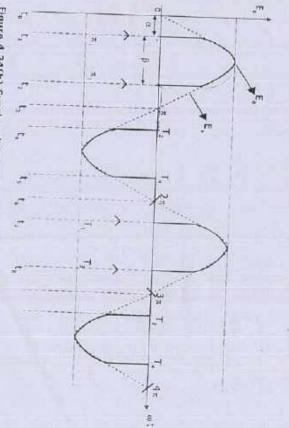

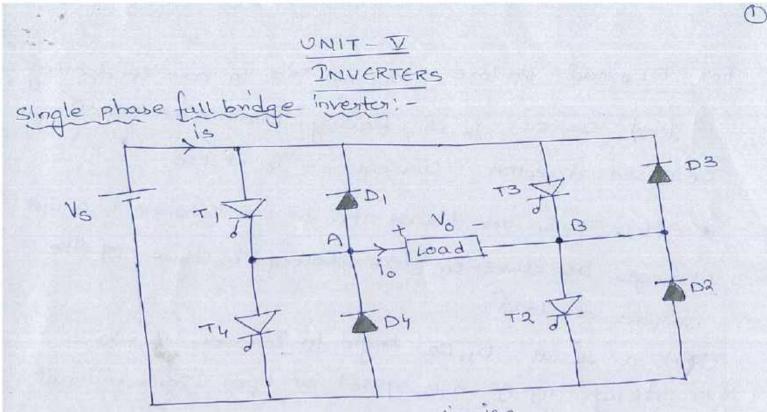

**Inverters**: Inverters Single phase inverter Basic series inverter, parallel Capacitor inverter, bridge inverter Waveforms, Voltage control techniques for inverters- Pulse width modulation techniques Numerical problems. Basics of Resonant Inverters.

#### Department of Electrical & Electronics Engineering

#### UNIT-IV

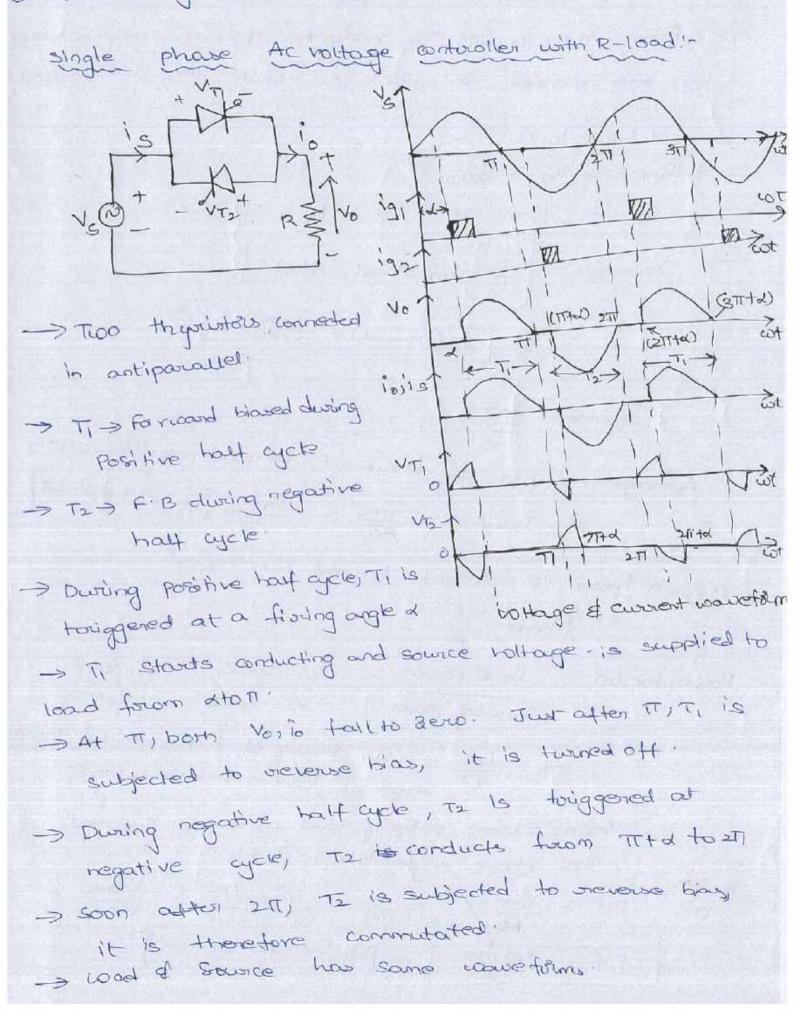

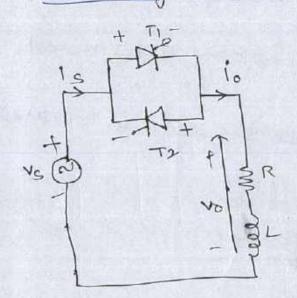

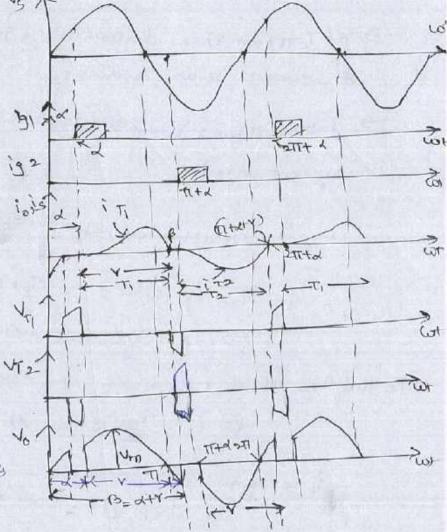

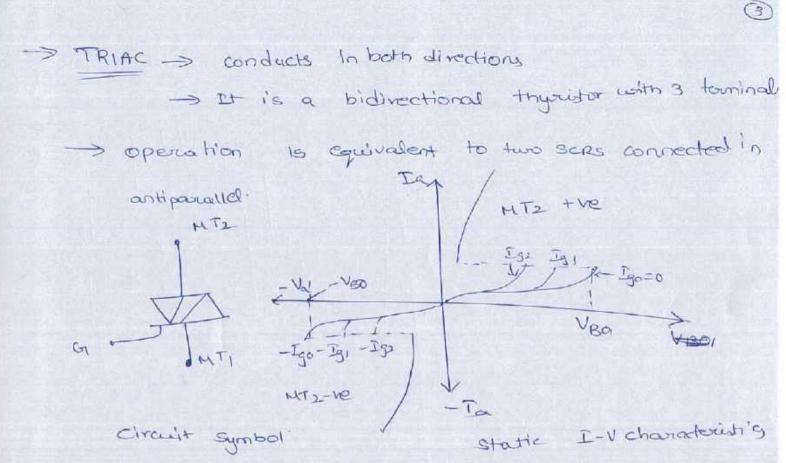

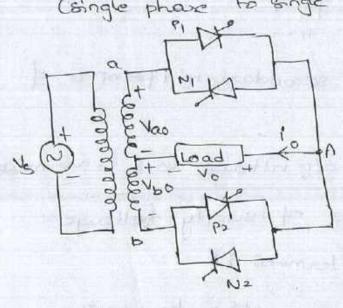

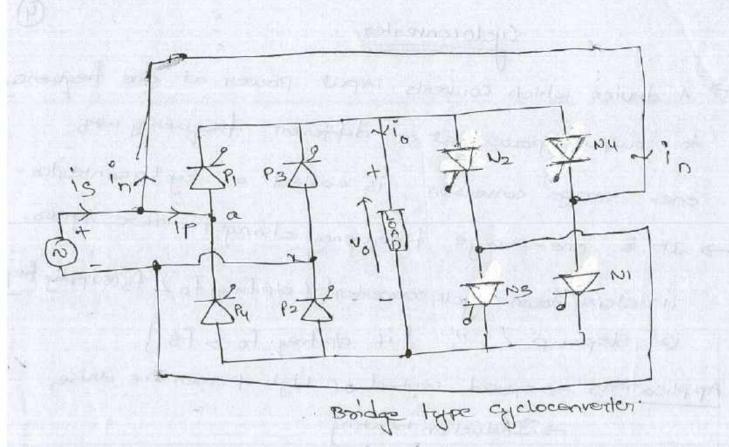

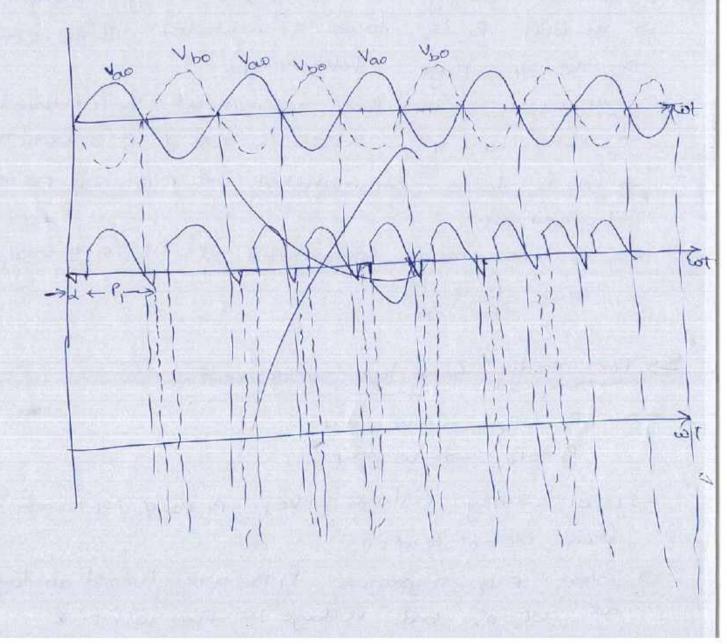

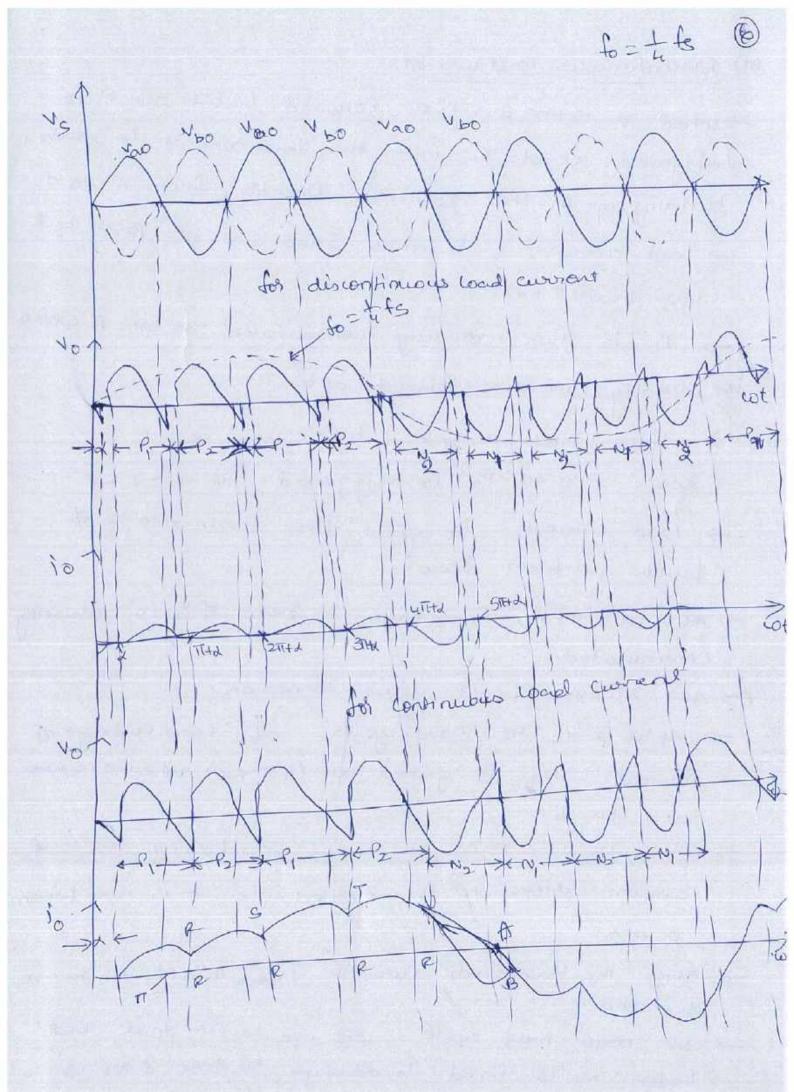

**AC Voltage Controllers &Cyclo Converters:** AC voltage controllers Single phase two SCR's in antiparallel with R and RL loads, modes of operation of TriacTriac with R and RL loads Derivation of RMS load voltage, current and power factor- waveforms, Numerical problems, Cyclo converters Single phase mid pointcyclo converters with Resistive and inductive load (Principle of operation only) Bridge configuration of single phase cyclo converter(Principle of operation only)Waveforms.

#### UNIT-V

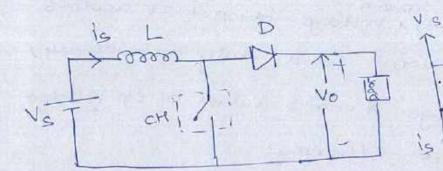

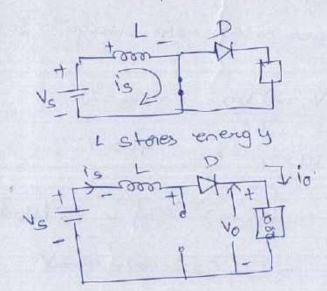

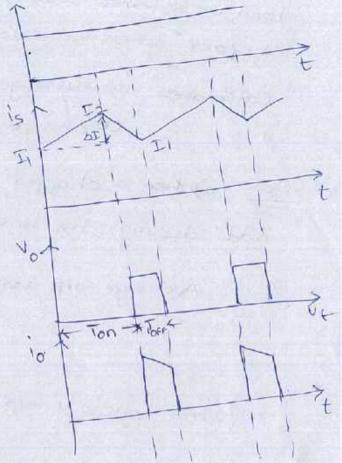

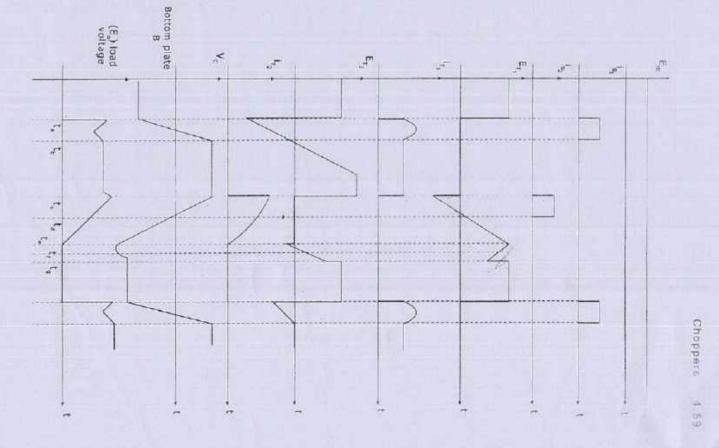

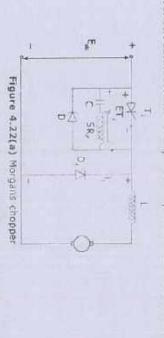

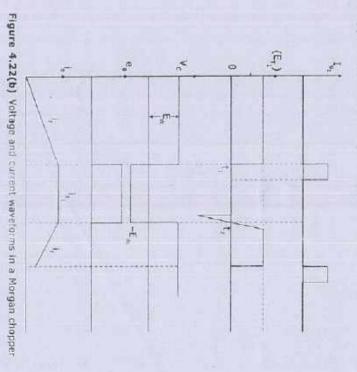

**Choppers**: Time ratio control and Current limit control strategies Step down choppers-Derivation of load voltage and currents with R, RL and RLE loads-Step up Chopper load voltage expression. Morgan's chopper Jones chopper Oscillation choppers (Principle of operation only) waveforms AC Chopper Problems.

#### **Text Books**

1. P.S.Bhimbra, "Power Electronics", Khanna publications.

2. M.D.Singh&K.B.Kanchandhani, Power Electronics, Tata McGrawHillPublishing company, 1998.

#### **Reference Books**

1. VedamSubramanyam, Power Electronicsby New Age International (P) Limited, Publishers

2. P.C.Sen, Power Electronics, Tata McGraw-Hill Publishing.

#### Department of Electrical & Electronics Engineering

#### **Power Electronics**

#### **CO-PO Mapping**

#### **Program Outcomes (PO)**

- 1. Ability to apply knowledge of mathematics, science, and engineering.

- 2. Ability to design and conduct experiments, as well as to analyze and interpret data.

- 3. Ability to design a system, component, or process to meet desired needs within realistic constraints such as economic, environmental, social, political, ethical, health and safety, manufacturability, and sustainability.

- 4. Ability to function on multi-disciplinary teams.

- 5. Ability to identify, formulates, and solves engineering problems.

- 6. Understanding of professional and ethical responsibility.

- 7. Ability to communicate effectively.

- 8. Broad education necessary to understand the impact of engineering solutions in a global, economic, environmental, and societal context.

- 9. Recognition of the need for, and an ability to engage in life-long learning.

- 10. Knowledge of contemporary issues.

- 11. Ability to utilize experimental, statistical and computational methods and tools necessary for engineering practice.

- 12. Graduates will demonstrate an ability to design electrical and electronic circuits, power electronics, power systems; electrical machines analyze and interpret data and also an ability to design digital and analog systems and programming them.

#### **Course Outcomes of Power Electronics:**

- 1. Discuss the basics of power electronic devices.

- 2. Construct the design and control of rectifiers, inverters.

- 3. Discover of power electronic converters in power control applications.

- 4. Compare characteristics of SCR, BJT, MOSFET and IGBT.

- 5. Demonstrate communication methods.

- 6. Experiment the design of AC voltage controller and Cyclo Converter.

- 7. Construct the Chopper circuits.

#### Department of Electrical & Electronics Engineering CO-PO Mapping

| Course   | Program Outcomes (PO) |   |   |   |   |   |   |   |   |    |    |    |

|----------|-----------------------|---|---|---|---|---|---|---|---|----|----|----|

| Outcomes | 1                     | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 |

| 1        | Н                     | Μ |   | Μ | Η |   | Μ |   | Μ | Μ  | Η  |    |

| 2        | Н                     |   | Η | Η | Н | Н |   |   | Μ |    | Η  |    |

| 3        | Н                     | Μ |   | Μ | Η |   | Н | Μ |   | Η  |    | Н  |

| 4        | Н                     |   | Н | Н |   | Μ | H | Н |   |    | Η  |    |

| 5        | Η                     | Η | Μ | Μ |   | Η |   | Μ |   | Μ  | Η  |    |

| 6        | Н                     | Н | Η | Η |   | Н | Μ | Η |   | Μ  |    | Η  |

| 7        | Н                     |   | Η | Н | Η | Н |   | Η | Μ |    | Μ  | Η  |

\* H: Strongly Correlating (3); M: Moderately Correlating (2); & L: Weakly Correlating (1);

# POWER ELECTRONICS

- INTRODUCTION. \* Power electronics combine the concepts of power, electronics

- + Power deals with the static and violating power equipme for generiation, triansmission and distribution of electric Power " anoniert beinsteater brie arely themselbert of

- \* Electronics deals with the solid state devices and circuits for signal pulcessing to meet the desired control objective \* It basically deals with power engineeoring is, generation transmission and distribution and utilization of electrical eneurgy at higher power levels \* P.E combines the aspects of electuaries engineering

- where efficiencies is not that important but the principles of control thus play a major viole is controlling power at higher levels and and all addition loss half

- + It is a subject that concerns the applications of electronic puintiples into situations that are mated at pould level rather than signal level.

- \* power electronics is based primarily on the switch. of the power semiconductor devices

"A subject that deals with the apparatus and equipment working on the principle of electronics but vated at paper level matter than signal level.

Some Applications of P.E

1. Acrospace: space shuttle power supplies, satellite power supplies, aincolaft power systems

- 2: Commencial: Adventising, hebting, airconditioning, central oreforigeoration, computer and affice equipment, uninterruptible power supplies, elevators, light dimmeous and flashers 3: Industrial: Airc and industrial furnaces blowers and forms, pumps and compressors, industrial laser, transformer top changeous, violling mills, textile mills, excavators (cenent mills), welding etc.

- excavators) cement mills, welding etc. 4. <u>Residential</u>: Airconditioning, lighting, space heating, refrig-- eviators, electric door openerus, duy evus, fans, personal Computors, vacuum cleaners, elc.

- 5: <u>Tele communication</u>: Botteny changers, power supplies 6: <u>Turansportation</u>: Batteny changers, treation control of electrical vehicles, electric locomotives, streat coros torolley buses, automotive electronics etc.

7. Utility systems: High voltage de transmission(HVDC), excitation systems VAR compensations static circuit breakers, fanss supplementary energy systems (solar, wind). Advantages of Power electronic convertery:-

unit-I (2)

-> Long life el less maintainance due to absence of moving parts.

-> Fast dynamic response of the pre systems as compared to electromechanical converter systems. -> small size and less weight result in less floor space and therefore lower installation cost.

-> mans pocoduction of semiconductor devices has resulted in lower cost of the converter equipment.

Disadvantages:

> they Power electronic converter arcuits have a knowing to generate harmonics in the supply system as well as In the load circuit.

as in the load circuit. > Acto de él ac to ac convertors operate at a low input powerfactor under certain operating conditions > p.e controllers have low overload capacity: > Regeneration of power is difficult in p.e converter systeme:

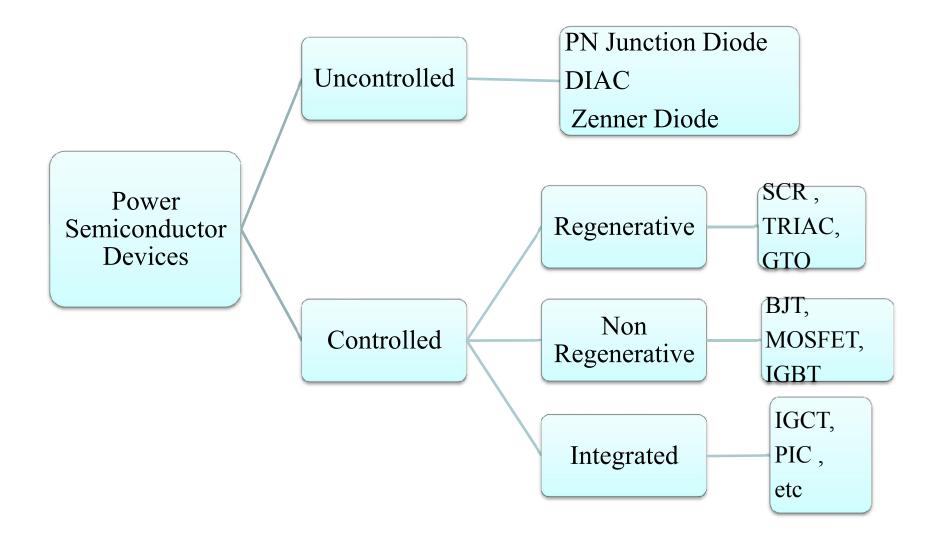

The advantages possessed by them for outpeightheir disadvantages mentioned above. As a consequence, semiconductor-based conventors are being entreme: extensitively employed in systems where power flow is to be regulat Eased on twom-ond twomoff chairs gate signal requirements idegree of controllability) the Proof semi conductor derices can be chassified as under in Diodes: These are uncontrolled meetifying devices. Their on & after states are controlled by power supply. Thyristors: These bave controlled twom-on by a gatesignal. After thyristors are on they remain blacked-in an-state due to internal inegenerative action & gateloss control these can be tranced off by power circuit.

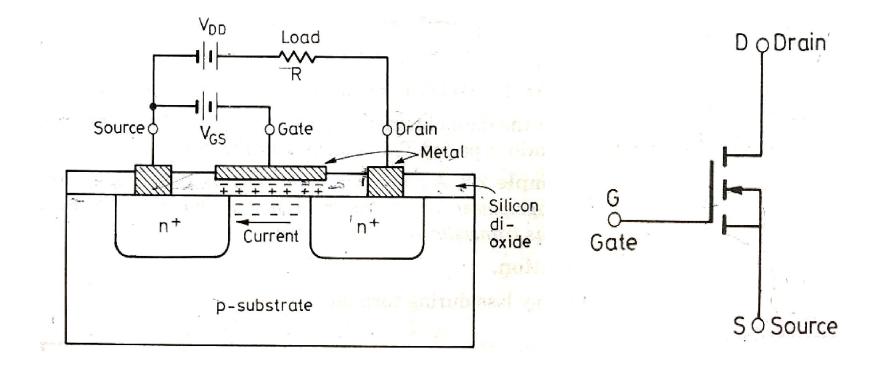

Controllable subtres: These devices are transdom & transdop by the application of control signals. eg: BJT, MOSFET GTO, SITH, IGBT, SIT & MCT.

Turiac & RCT possess bidirectional connent capebility whereas all other remaining devices (diade, SCRIGTO, BJT, MOSFET, IGBT, SITH, SIT &MCT) are unidirectional correct devices.

# TYPES OF POWER ELECTRONIC CONVERTERS

-> A P.E system consists of one or more p.E converteus -> A P.E converter is made up of some power semiconduction devices controlled by integrated dravits.

-> the P.E (onventors (or circuits) can be classified into

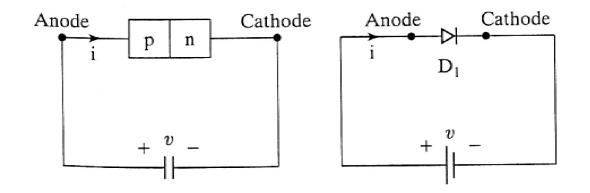

sin types. 1. Diode Rectifier: A diode rectifier circuit Converts ac input Voltage Into a fixed de voltage. The ilp voltage may be single phase or three phase. They are used in electric traction, battery charging, electro plating, power supplies, UPS; voelding etc.

and constant and an endager was first and and the state of

oK

200

25004 500 A 100.0

1200V/40A 20.0

1200V/1000A 0.50

0

0

(26)

P

5

PD

S

(b) MOSFET (n-channel)

(D) SIT Go Static Induction transistor

Ċ Gi

(d) IGBT

Insulated make Elpolor translator 1000V/50A 100'0

1200V 300A 100.0

1200 V 500A 50'0

#### wit-I 3

2: Ac to de converteus (phase - controlled vectifieus): - These convert constant ac voltage to voulable de autput Voltage: these are used in de arrives chemical industries, excitation systems for synchronous machinese

# 3. De to De conventors (De choppers)

A de chopper converts fixed de input voltage to a controllable de output voltage the chopper ext require forced, or load commutation to twinoff livits -> used in de drives, battory driven vehicles, brolley towers etc.

# 4. De to ac convertors (inventors)

An inventor converts fixed de Voltage to a varia--ble ac voltage. The olp may be variable voltage or volviable frequency. It requires line, load or forced commutation for twing-eff the tryristors ->use in induction-motor, synchronous motordouves, induction heating, UPS, HVDCT etc.

5. Ac to ac convertous: These convert fixed ac input voltage into variable ac output voltage. These are of two types

as under. (a) <u>Ac voltage controllers (Ac voltage regulators</u>) : converts fixed ac voltage directly to a variable of voltage at

the same frequency. (b) <u>cycloconverters</u>? These circuits converts ilp power at one frequency to output power at a different frequency through one stage convertion. 6. <u>static</u> <u>subtches</u>: The power semiconductor devices can open it as static <u>suitches</u> or contactors: static <u>subtches</u> possess many advantages over mechanical and electromechanical circuit Breakers:

e anapputo to antentra con duppeno

A de chieppen converte l'étent de l'épar volte q le le contrationne de contrat voltage stat chieppen des veguine londeds en toor contrationée le bunnels les puedes als vez bortens contration etheles sector

An investor converter and the vertex to vertex to vertex to the sector t

6. At to a convertory i there canned there a time and you with the second part of the sec

Land Ac sothing automore ( acting setting setting to a loss a land a setting a setting of setting a land a setting a

the approximation other chically converts in price at a sufficient for any the angle at a different formers the approximation in the price of the convertion in the convertion

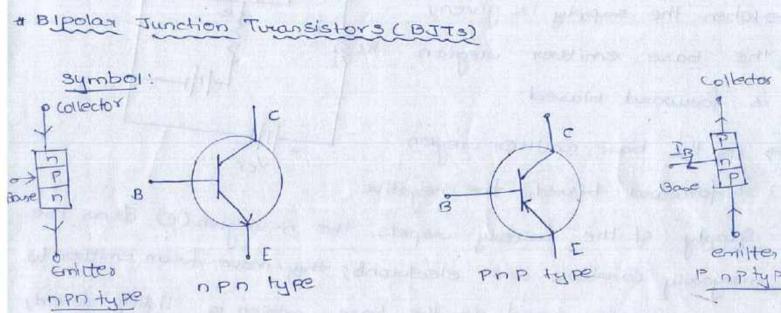

POWER SEMILCONDUCTOR DEVICES

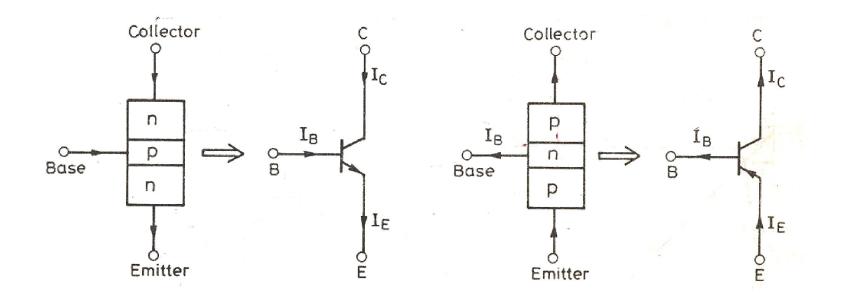

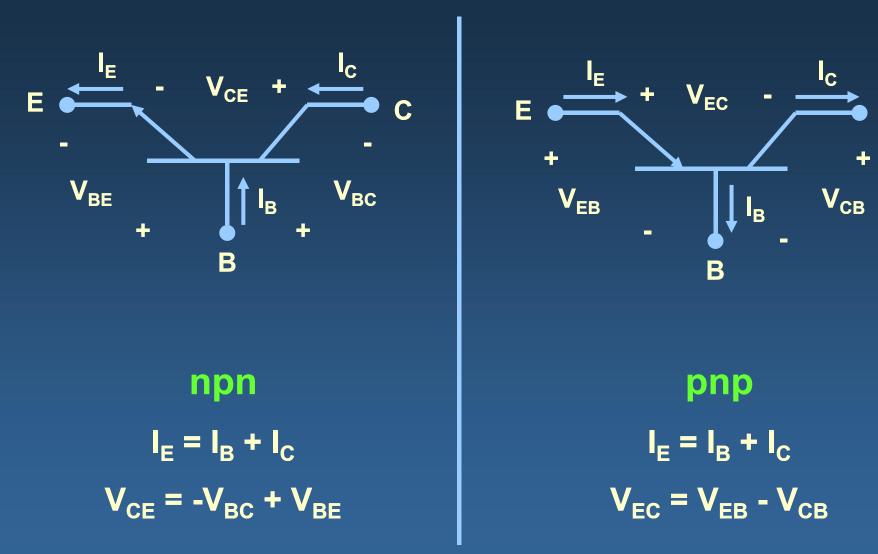

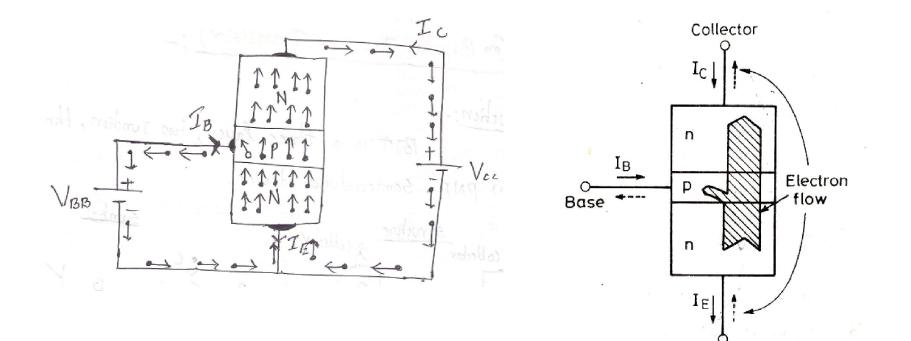

> Those layer, two junction npn or pop semiconductor device. > with one puregion sandwiched by two n-regions, npn tra - nsistor is obtained

-> with one two p- regions soundwiched one n- region, Pnp transistor is obtained.

> the term Bipolon denotes that the connect flow in the device is due to the movement of both holes of electrons -> A BIT has three terminals named collectoric), entitlede & Base (B)

-> use of power npn transistors is very wide in very wide in high-voltage and high ament applications. -> BST is amient continuited device. -> PRINCIPLE OF OPERATION:

> NPN -> > when the supply is given, the base emitter sugion is forward blased

> As the base enviter region \_\_\_\_\_\_ Vec is forward biased, the negative

Supply of the batteory repets the n-region (E) & as the majority corriers are electrons; they more from emitter to base megion and as the base region is lightly doped, Some of the electrons combine with holes and then remain -ning enter into the collector megion as it is heavily doped and large amount of associat flows in the callector

segion The Base Current IB is given by

The currents IE, IB & Ic are assumed positive when the they enter into the townsistor.

IB

Vbez > Vce,

Vice, Voez

38 stand unlarged

411-100

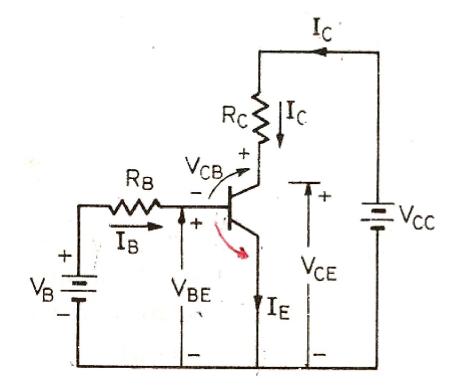

CHARACTERISTICS Steady state characteristics Input characteristics: The Input characteristics are duraion between the base emilier voltage and base current by keeping

the value of the collector childworldge

to a constant value.

UNA-I (5)

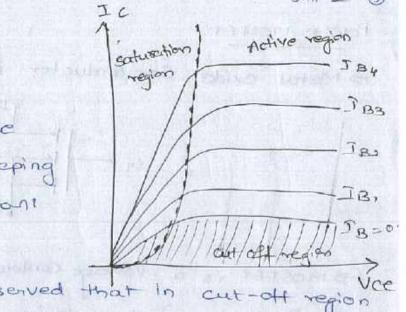

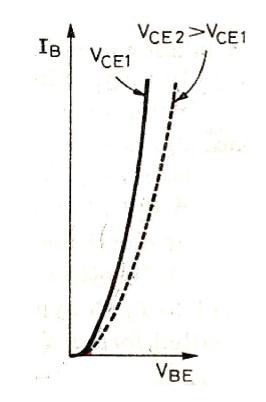

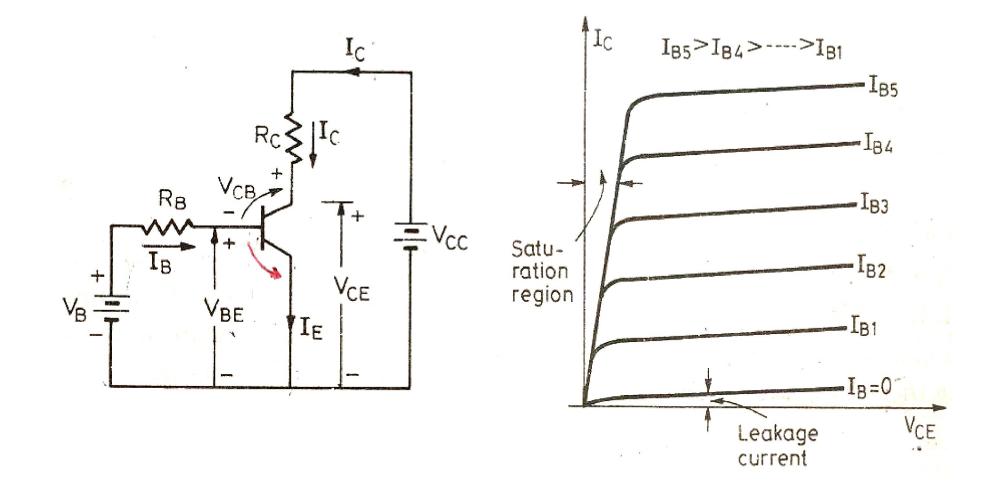

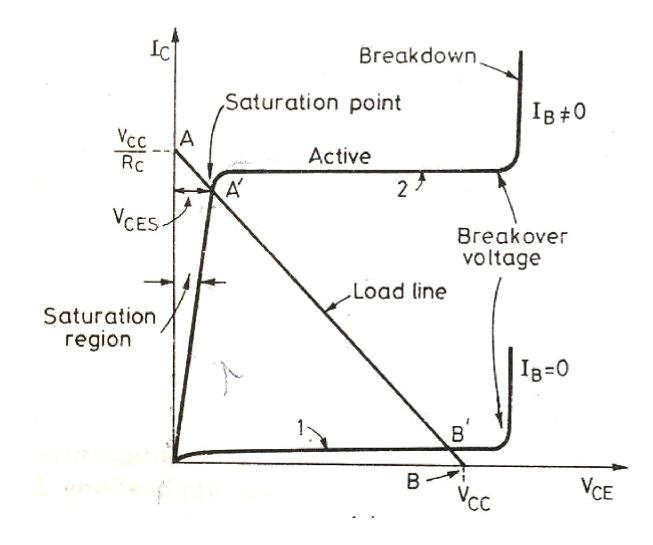

Output characteristics :

IB4>IB3>IB>>IB1>IB

The output characteristics and drawn between VCE and Ic keeping the base current to a constant value

From the graph, it is observed that in cut-off region the voltage is high and the current is less and in the saturation region , the current is high and the voltag is less:

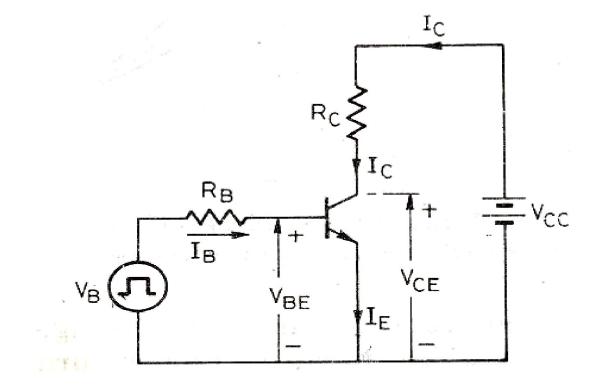

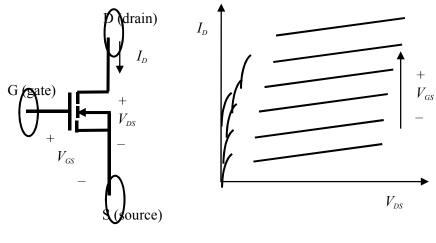

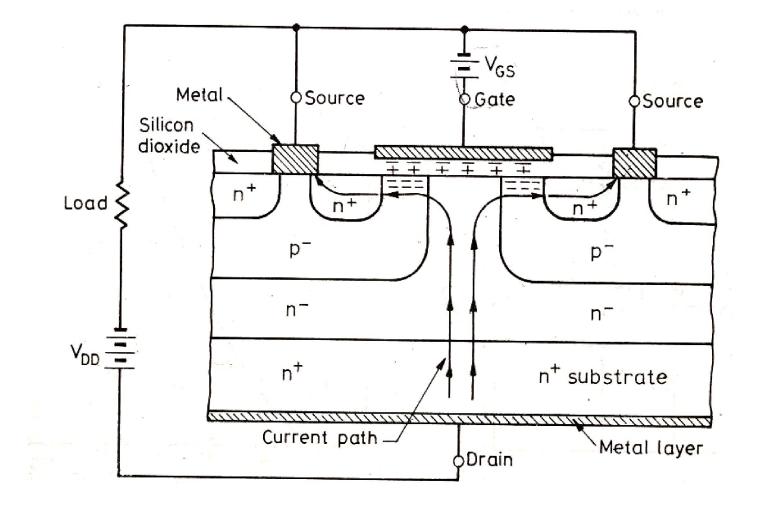

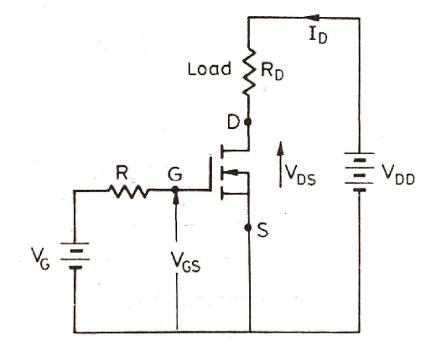

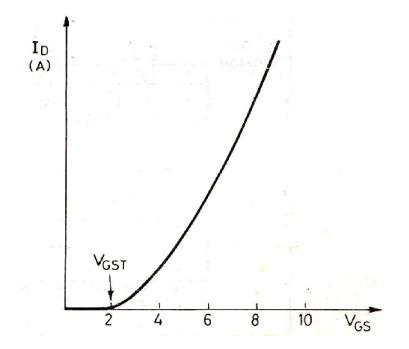

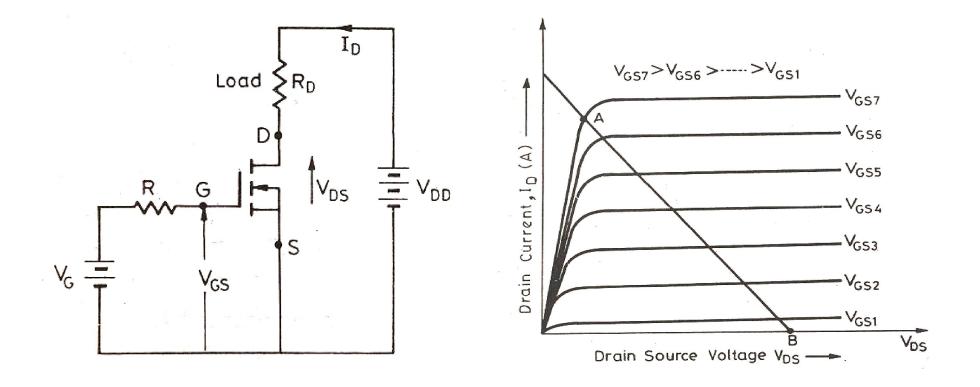

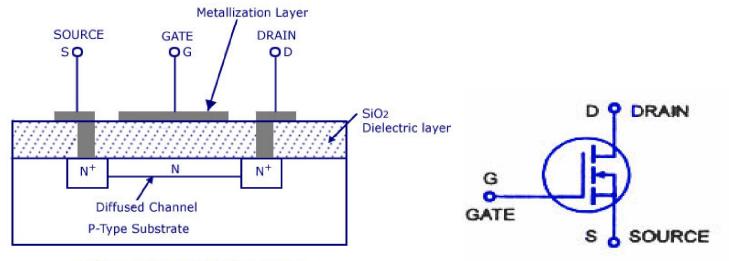

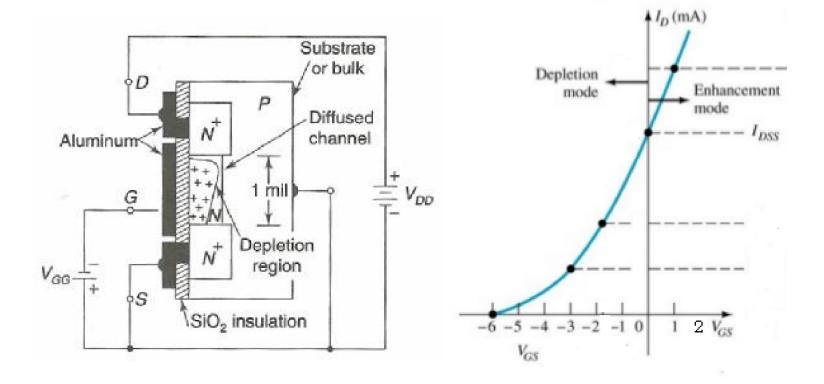

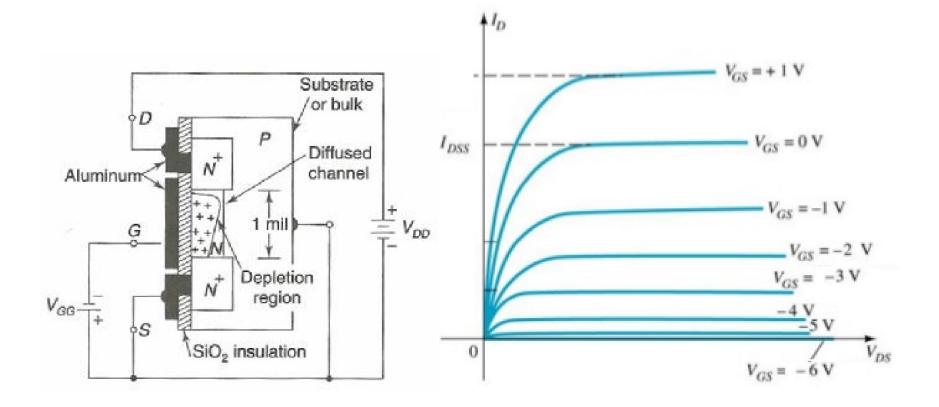

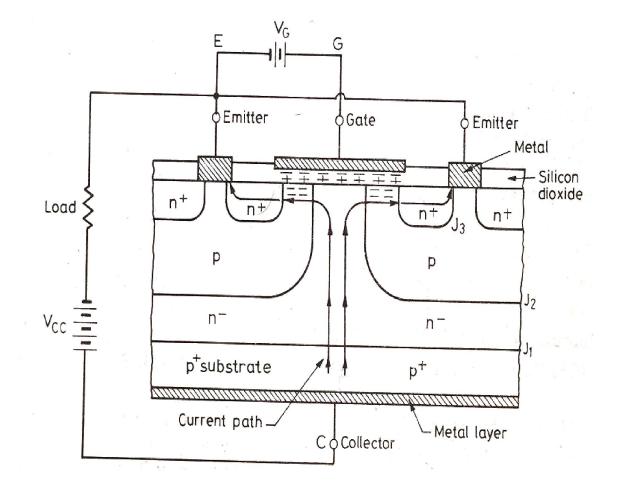

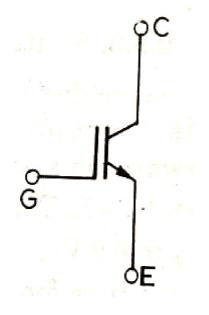

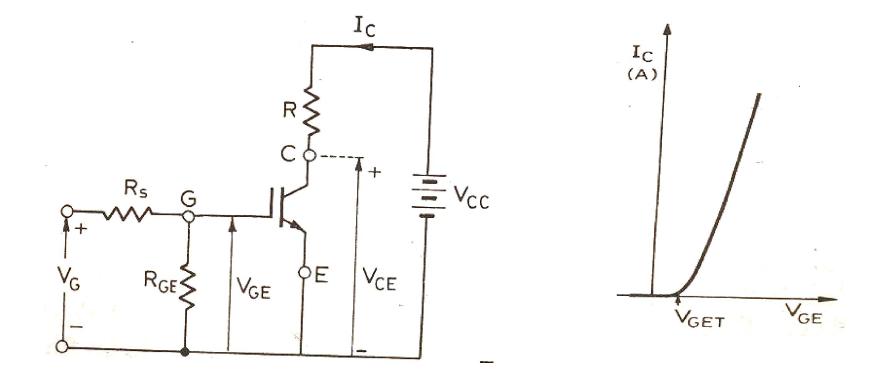

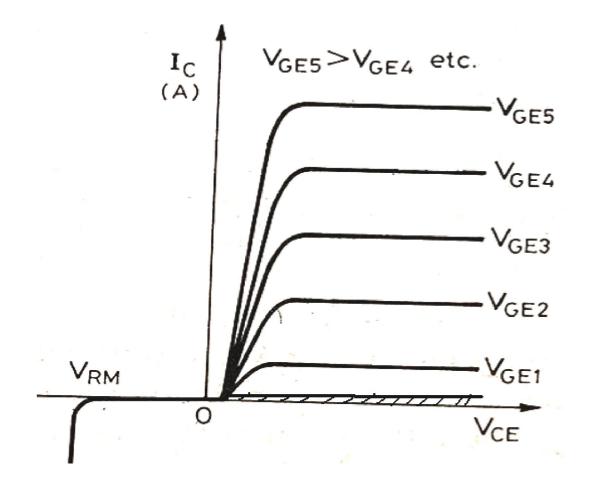

Switching characteristics In transient condition the forward blased PN'sunction exhibits two parallel copacitances: A depletion layer capacitance and a diffusion copacitance of a reverse blased P-n'suchion has only depletion Capacitance. Under transient conditions, they influence the twing n & two off behaviour of the translates. POWER MOSFET!

definitions to hondulo Semiconductor Field Effecting transistor. > Metal Oxide -> It has three terminals (i) Drain(D) G K (ii) Source(s)

a voltage controlled derice. > MOS FET

> It is a unipolar device.

-> The Grate circuit impedance in MOSFET is extremely high of the order of 109\_2, hence the base current of required in MOSFET is much lesser than the control signal or base current required in BJT. -> The large impedance permits the Moster gate to be driven directly from microelectronic circuits. -> Power MOSFETS are now finding increasing applications in differing and plan series low power high frequency converters > Two types \_ > n-channel HOSFET > more commonly used : of higher mobility of electrons. > P-channel MOSFET

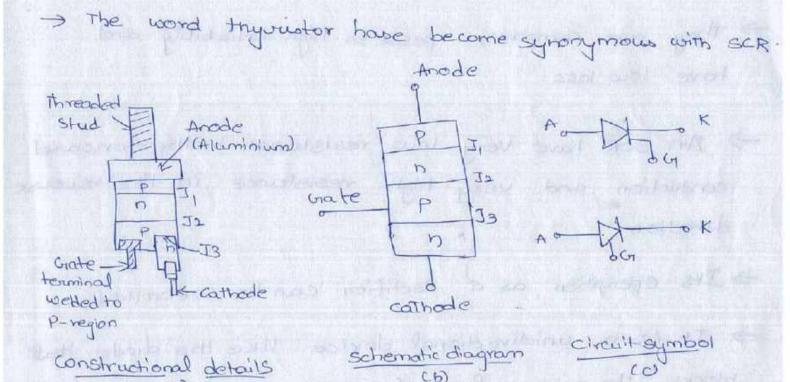

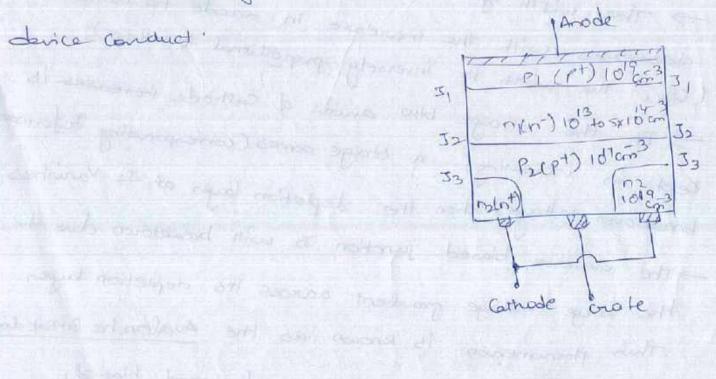

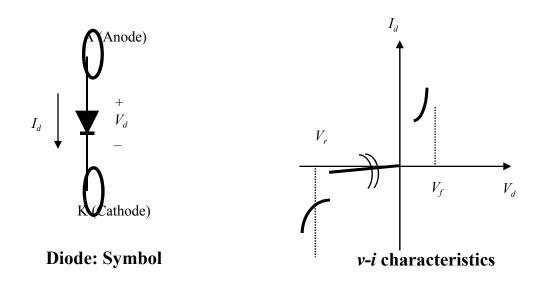

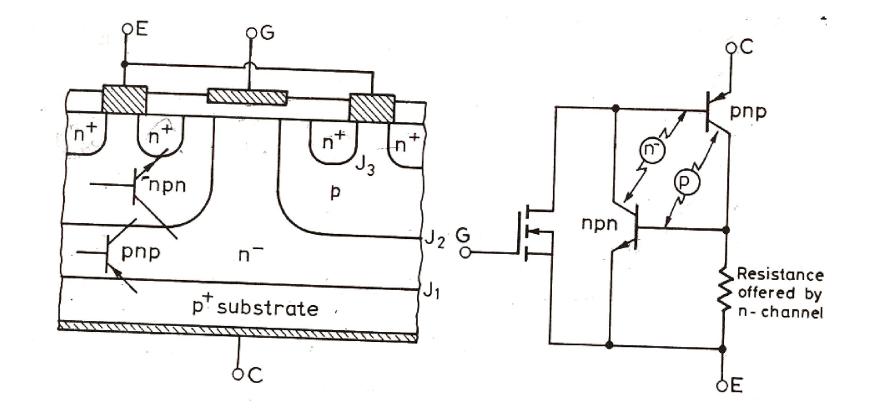

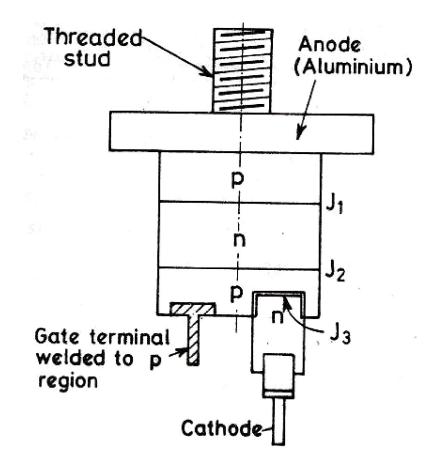

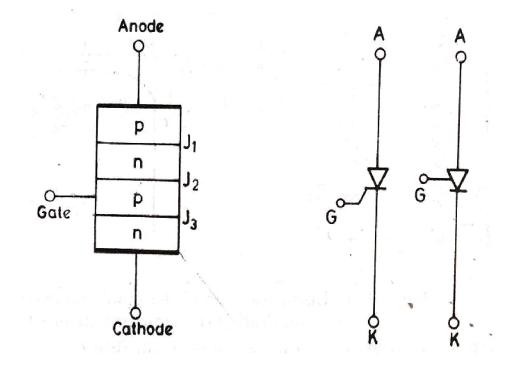

## THYRISTORS

(0)

> Bell laborraboules were to fabricate a the first silicon - based device called Thy pristor Semiconductor -> An oldestimember thyvis tor of this family, called silicon - controlled most widely Rectifier (SCR), is the used device .

The terminal connected to outer a region is called Cathodelk and that connected to inner pregion is called crote(Gr). > For large current applications, thynistoxs need better cooling, by mounting them on to test sinks.

by mounting them on to test sinks. > SCRS of voltage rating IOKV and an sums current wating of 3000 with corresponding power-handling capacity of 30MW are available.

> They are compact, possess high reliability and have low loss.

> IAM SCR have very low resistance in the forward conduction and very high resistance in the reverse direction:

→ It's a unidivectional device. Like the diode, that blocks the current flow from cathode to anode. → Unlike the diade, a linguistor also blocks the current flow from anode to cathode until it is toggened into conduction by a proper gate signal between gate & cathode

balles at water 1 water of ballantics . I fortunat with a

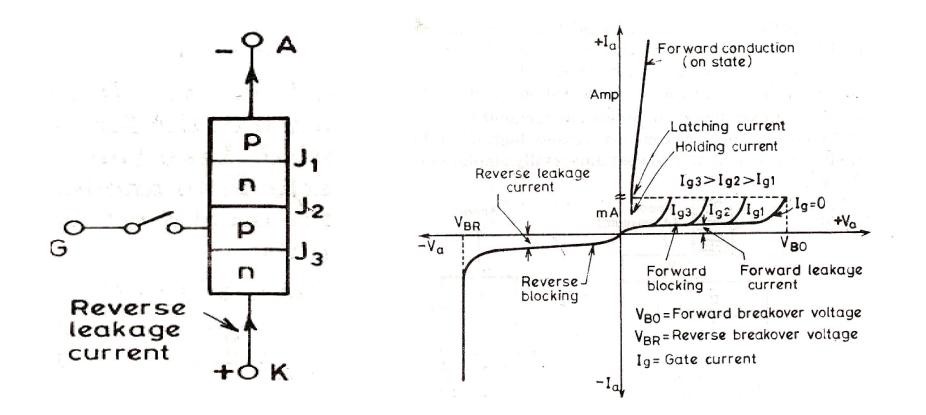

Puinciple of operation:

- -> The Hyristor operates in three modes

- (i) Revenue blocking mode

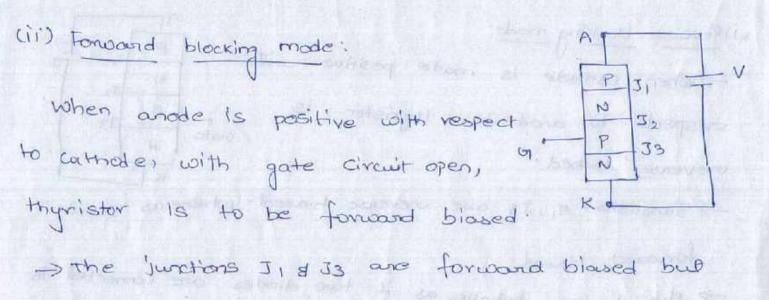

- (iii) Forward blocking mode

- (iii) Forward conducting mode

cilReverse blocking mode: -> when carbode is made positive with PJJ = unespects to anode the thyristor is P Chate vievense biased. -> Junctions J1, J3 are oreverse biased. where as J2 is

forward biased. -> The device behaves as if two diodes are connected in Series with revenue voltage applied across them -> A small leakage content of the order of a few mA or ut flows T

unit

12

-> this is called revenue blocking made, called off-state of the thysistor.

> If the reverse voltage is increased, then at coultical breakdown levels called neverse breakdown voltage VBR, an avalanche occurs at J & J3 & the veverse current increase scapidly.

-> A large current associated with VBR gives vise to note losses in the SCR.

- This may lead to thyristor damage as the junction temperature is may exceed its permissible temperature vulse.

- > Hence manimum working reverse voltage does not exceed VBR.

Junction J2 is neverse blased.

> In this mode a small lakage current flows called forward leakage current, sore oftens high impedance > : thyristor can be treakted as an open subtch even in the forward blocking mode.

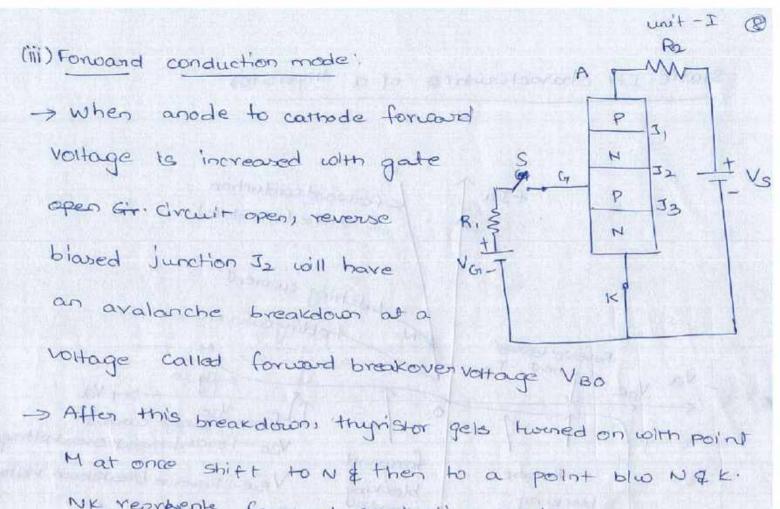

> fit we exceed the voltage beyond the forward break over voltage theo it permanently abroages the device].

NK represents forward conducting mode.

> A Pothysistor can be brought from forwoord blocking made to forward coinduction made by twrning It on by applying (i) a positive gate pulse between gate and cathode

> or (iii) a forcourd break over voltage acutoss anode and cathode.

-> when we give the gale current with cathode then the device enters forward conducting mode. (when switch sig closed infi -> In this mode, thyristoris theated as a closed switch.

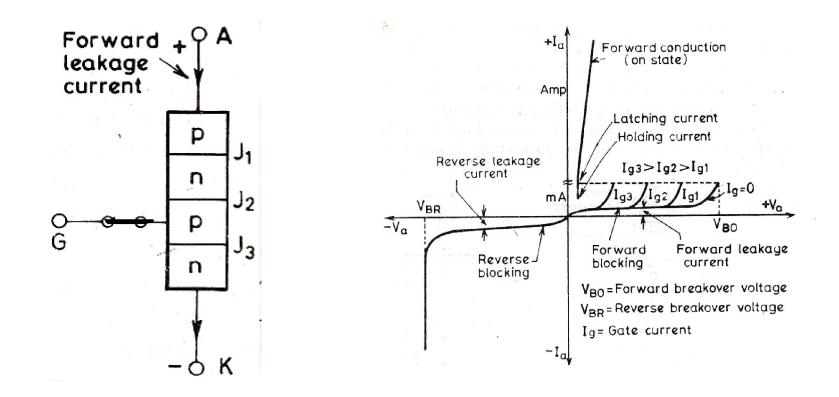

th) Fondand conduction for Static I-V characteristics of a thyristor - Forward corduction +Ia (on-slate) and an ange E mailward current tobling curr end N. Revenue leakage TBO. Ig =0 Va VBR >+ Va TL Forward Leakage curvers 0 note musth E. inochal V30 - Forward break over voltage 2 forward VBR- Reverse breakdown voltag d sta w blocking Ig - gate current Plock 0 -Ja Jack Sol and missinger stori stop by lacq o (i) spot ungo 5 borthod bone accrede apportantes and manua sing sut any au nable and shart pa diffice based a se betond a different is bour side it.

A day Pa

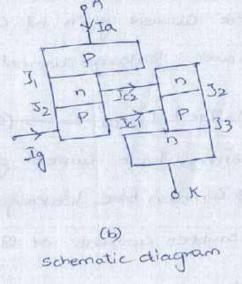

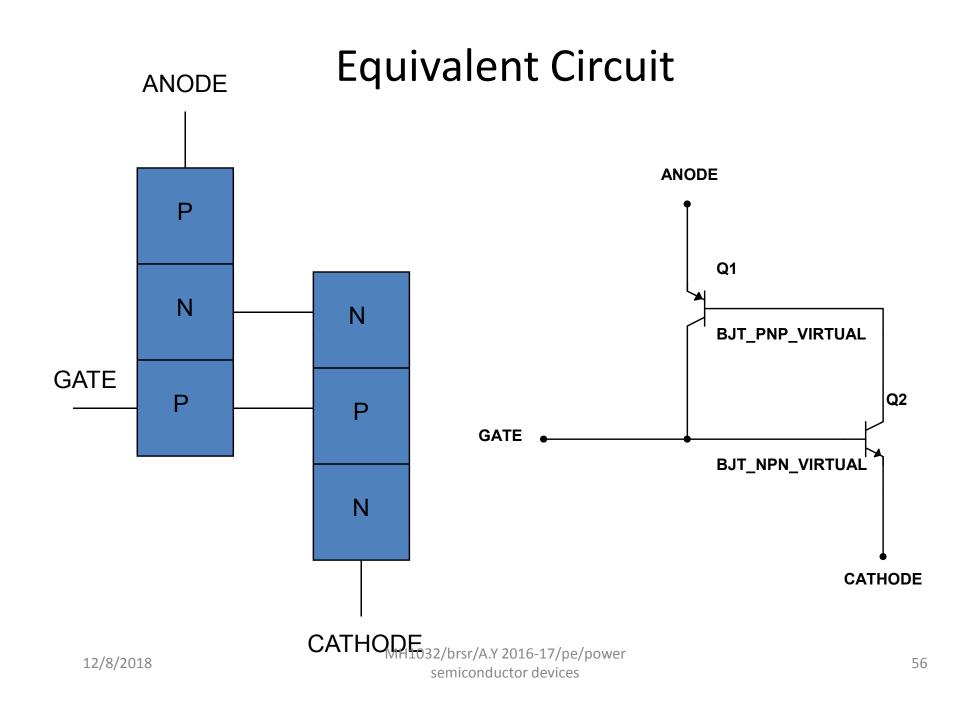

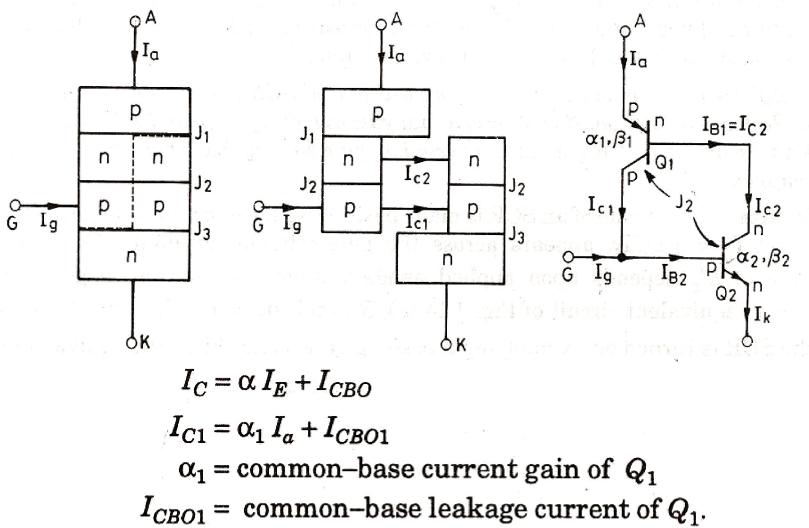

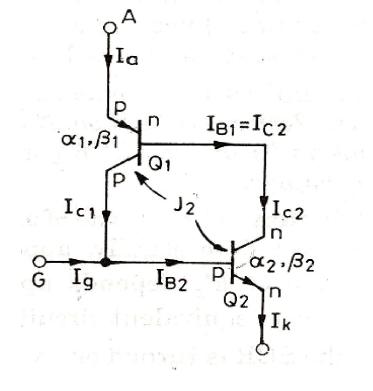

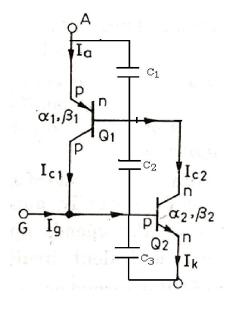

Two transistor model of thyristor.

Two toransistor model

dispi In IBI=Jez

Ig IB2 B2 T

(2)

P 32 102

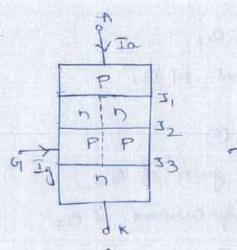

> The puinciple of thyvistal openation can be explained with the use of its two-townsistor madel (or two transistor

-> The Junctions J1-J2 and J2-J3 can be considered to Constitute prp and npn tocansistors seperately.

-> The Gravit representation of the two transistor model of a thynistor is shown in fig.

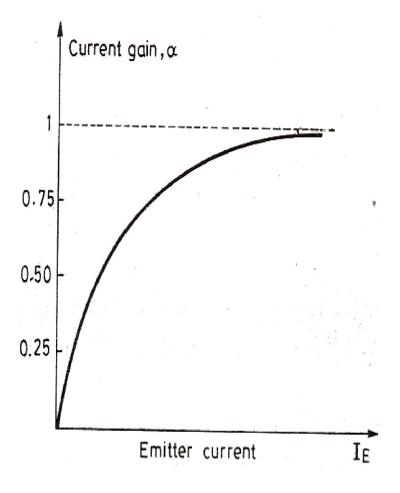

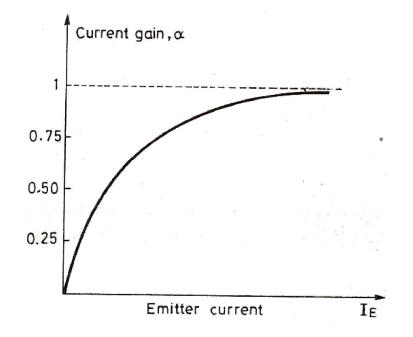

-> In off-state of a toronolotor, collector current Ic is crelated to envitter current IE as ist B greadean mi

Jc= «JG+ JCBO

where of is common base current gain

Iceo is the common have leakage awarent of collector-base jurction et a triansistor.

-> from tigic, for os, transistor, IE = anode connert Iq  $T_{C} = T_{C_1}$

$$\begin{aligned} F_{C1} = 4F_{C1} + F_{C100} \longrightarrow 0 \\ F_{C1} = 4F_{C1} + F_{C100} \longrightarrow 0 \\ f_{13} \otimes ammon base avoid gain of G, \\ F_{C201} \otimes ammon base avoid gain of G, \\ F_{C201} \otimes ammon base avoid gain of G, \\ F_{C201} \otimes ammon base avoid gain of G, \\ F_{C201} \otimes ammon base avoid gain of G, \\ F_{C201} \otimes ammon base avoid gain of G, \\ F_{C201} \otimes ammon base avoid gain of G, \\ F_{C201} \otimes ammon base avoid gain of G, \\ F_{C201} \otimes ammon base avoid gain of G, \\ F_{C201} \otimes ammon base avoid gain of G, \\ F_{C201} \otimes ammon base avoid for G, \\ F_{C201} \otimes ammon bavoid for G, \\ F_{C201} \otimes ammon base avoid for G, \\ F_{C201} \otimes ammo$$

# THYRISTOR TURN-ON METHODS:

> with made positive with respect to cathode, a thyristor can twind on by any one of the following techniques.

Unit-T

(a) Forward voltage toriggeoring

(b) wate turiggering

(d) temperature buiggering

ce) light buiggering.

(a) Forward voltage touggering!

-> When forward voltage 15 applied between anale and cathode with gate chrewit open, Junction J2 is neverse blased.

-> As a viesuit, depletion layer is formed accross Junction J -> The width of the layer decreases with an increase in anode-cathode voltage

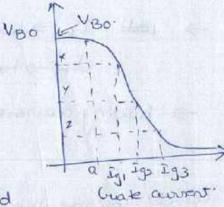

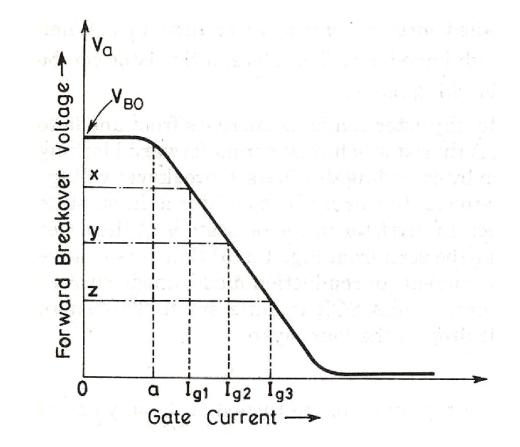

>If forward voltage awwas anode-cathode is gradually increased, a stage comes when the depletion layer across J2 Vanishes, J2 is said to have avalanche breakdown and the voltage at which it occurs is called forward Breakove, voltage VBO

> As the junctions J1, J3 are already forward biased, breakdown of J2 allows free movement of capitiens across three i sunctions and as a viesuit, large forward and e-- current flows.

-> The forward current is limited by the load impedance. -> In practice, the triansition forom off-state to on-state Obtained by exceeding VBO is never employed as it may destroy the device.

> VBO is taken as final vortage viating of the device during the design of sce applications

→ After avalanche breakdown, 52 loses its reverse blocking capability: i if anode voltage is reduced below Viso, SCR will continue conduction of the current. → The SCR can now be twened off only by neducing anode current below a certain value called 'holding current'

(b) trate triggering :-

-> This Tuning on of thyristors by gate briggering is Simple, welliable and efficients most usual method. > A positive gate voltage between gate and cathodo is applied.

-> NOITH gat currents a posi changes are injected into the inner Player and voltage at which the forward breakever occurs 18 reduced:

-> The forward voltage at which the device switches to On-state depends upon the magnitude of gate current ->once the scr is conducting a forward current, neverse biased junction II no

longen exists.

-> As such, no gate autorent is orequired for the device to remain in on-state.

lifthe gate content is removed, the conduction of content from anode to calmode remains unaffected.

→ If gale current is reduced to zero before the hising anode current attains a value, called the latching current, the thypistor will two-off again.

> The gate pulse width should therefore be judiciously chosen to ensure that anote currient vises above the latching

avosent. -> Latching convent: may be defined as the minimum value of anode avoient which it must attain duoing how -on purocess to maintain conduction when gale signal is remove

> The thysistor can be twined off only if the forward worker fails below a low-level worker called the holding current.

->Holding current' may be defined as the minimum value of anode current below which it must fall for twoming-off the thyristor.

> IL>IH. > Let IL>twoon IH > two off.

> holding current , in industrials applications is almost takenase zero.

- (c) <u>dv</u> toniggeoring.

- -> with forward voltage across the ander and cathode of a thyrites, the two outer junction J1/J3 are forward based J2 is vererse blaced.

- -> J2 has the characteristics of a capacitor due to charges existing across the junction

- -> The space changes cruist in the depletion region resultance

- => Ip forward voltage suddenly applied, a charging current through Junction capacitance (j may two on scr on the

- -> Almost the entire Suddenly applied forward rollage Va appears across Junchion 32

the changing convert ic =

$$\frac{dQ}{dt} = \frac{d}{dt}(G) Va$$

=  $C_j \frac{dVa}{dt} + Va \frac{dC_j}{dt}$ .

As the junction capacitance is constant, di =0.

inte= cjdVa.

if ante of ruse of forward witage dvalde is high, Ic would be more the period because when more -> This changing amount is play the mole of gate current & turns on the sch even thoughgate signal us zero

-> Note: even if Va is small, it is the mate of change of 1/4 that plays the vole of turing on the device. (d) Temperature tougering:

-> During F.B mode, most of applied voltage appears acoross oreverse junction 32

-> This voltage across, J2, associated with leakage avoient, would vise the tenperature of this junction Dwith Increase in temperature, width of depletion layer decreases. This further leads to more leakage curred 1) athick there. fore, more inclien temperature -> with cumulative process, at some high temperature

(within safe limits), depletion layer of viewerse blowed Junchion variables and the device gets twined on .

12 paras sull 211 - Langa

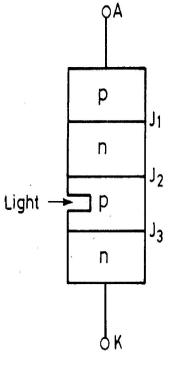

(e) light triggering ...

→ For light truggered scrs, a necess(orniche) Is made in the Inner P-layer. >It this recers is is is is invadiated, free charge n 33 courriers are generated.

-> If the intensity of this light throws on the receiverceds a certain value, forward biased ser is truned on Wed in HVDCT. (advantage of electrical isolation between power and control circuits)

Twinoff:

-> commutation is defined as the process of twoning-off a trypristog.

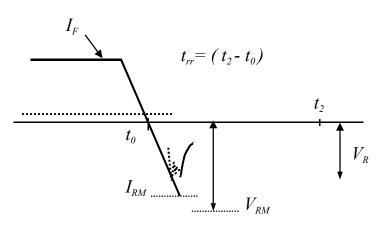

Dynamic or switching characteristics of thynistor

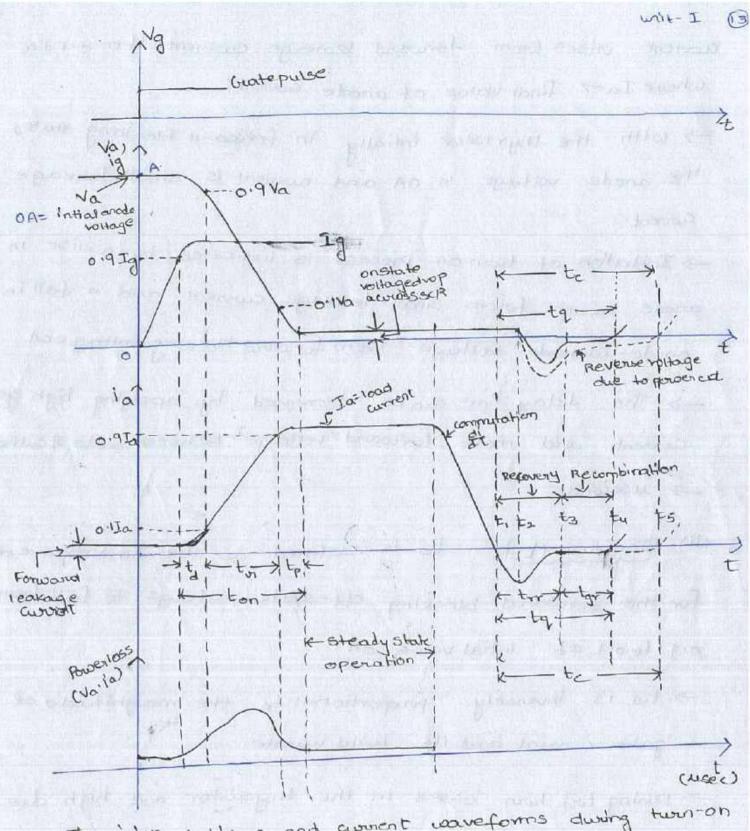

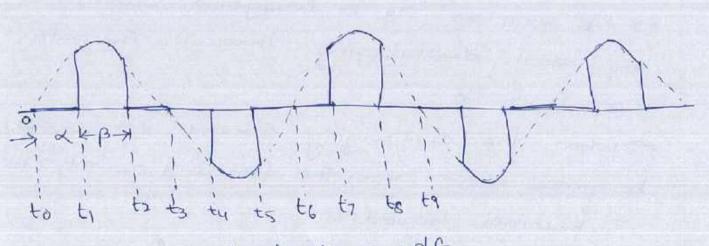

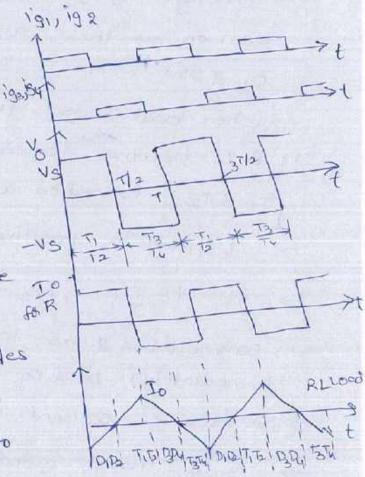

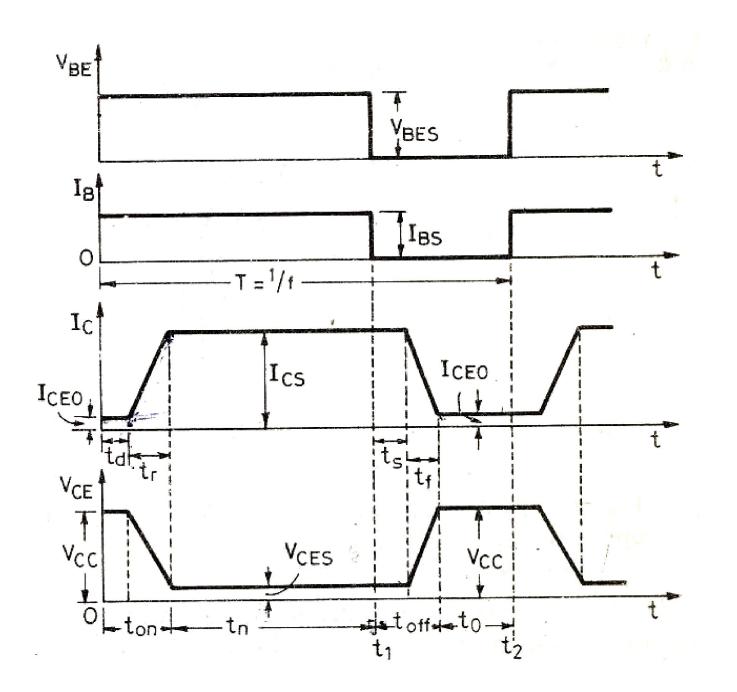

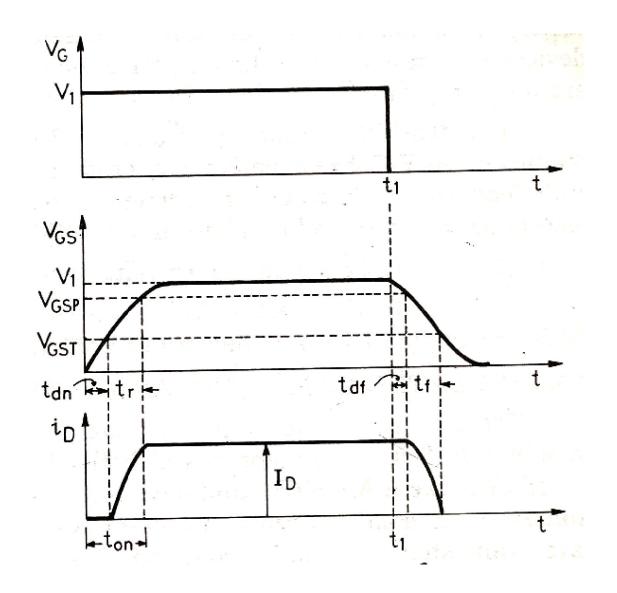

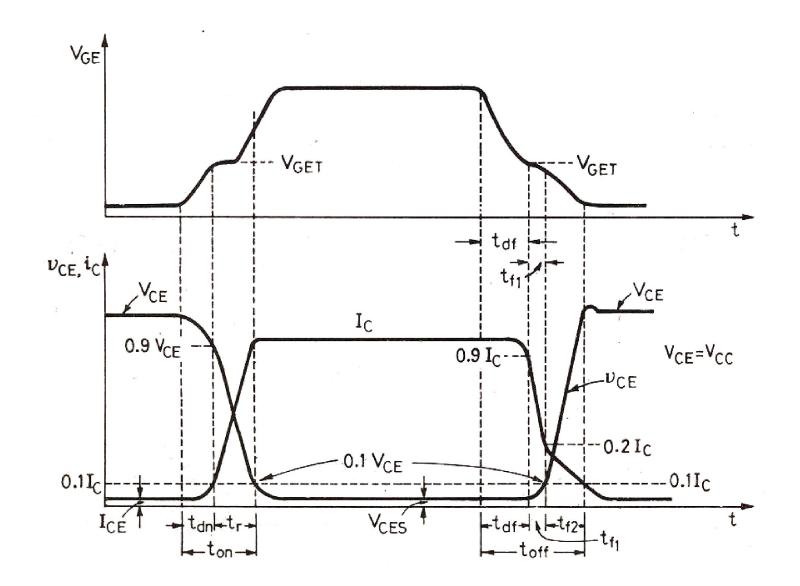

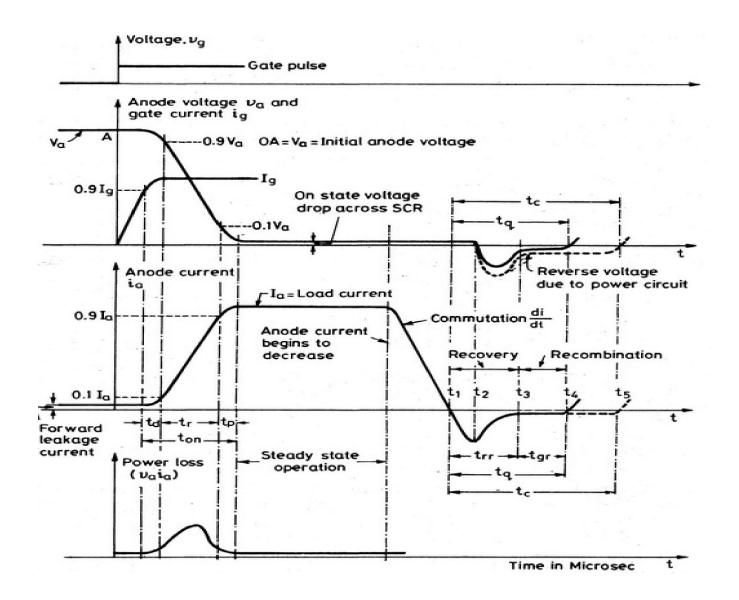

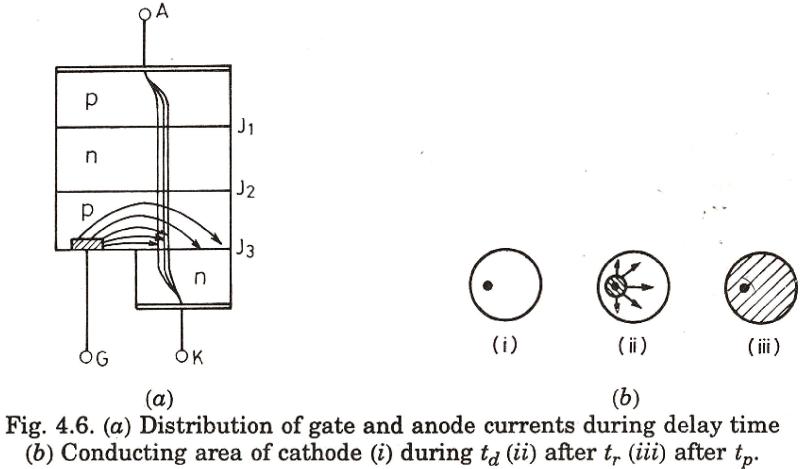

-> During turn-on & turn-off publicesses, a thyrustor is subjected to different voltages across it & different converts through it -> The time variations of the nottage across a thyristor of the convert through it during two-on of two-off processes give the dynamic or switching characteristic of a thyristos (a) switching charactuistics during two-on:-Then A transition time forom forward off-state to Sonward on-state called thyristo, turnon time, is defined as the time during which it changes from forward blocking stole to final on-state. -> Tuan-on time can be divided into those intorvals. inderay time to. in the data of and (iii) spread time tp (ii) use time to

Thyoustor voltage and connect vareforms during two-on and two-off processes.

## Twinon

is Delaytime ta: ta is defined as the time during which and voltage fails forom one Va to orgva where Va > initial value of anode voltage. (03)

to is defined as the time during which anode

connent vises from forward leakage connent to 0.1 Ia: where Ia-> final value of anode connent.

-> with the thyristor initially in forward blocking states the anode voltage is OA and coverent is small leakage covent.

-> Initiation of twomon process is indicated by a ribe in anode awarent forom small leakage awarent and a fall in anode-cathode voltage from forward blocking voltage of -> The delay time can be decreased by applying high gate Current and more forward voltage between anode exceptioned

-> usecondo.

(ii) Rise time (Ed):- to is defined as the time required for the forward blocking off-state valage to fall from org to oil of initial value off.

-> tor is inversely proportional to the maightfude of gate warmant and its build uprate.

-> During tor, two losses in the thyristor are high due to high Va & Jaigh Ia occuring together in thyristor

(TTP) Spread time (tp) :- tp is the time taken by the anode worked to use from 0.9 to Ia. (or) It is the time for the tonoard blocking voltage to fail from 0.1 to its initial value to on-state drop.

anasonal the need have

## wit-I (4)

-> After the spread time, and a connect attains steady state value and the voltage doucp acouss scr is equal to the on-state voltage docop of the order of 1 to 1.5V.

-> Tran on time of an SCR is equal to sum of delay time, visetime and spread time.

-> Total two on time depends upon anode act parameters & the gale signal volveshapes

-> Turn on time can be useduced by using higher values of gate currents.

Scottening characteristics during Turn-off:-

> The dynamic process of the scr from conduction state to forward blocking state is called commutation process or hurs-off process

-> once the thysistor Ison, gate loses control -> scr can be trained off by meducing the anode coment below holding concent:

> The two-off time top of a thypuistor defined as the time between the instant anode courant becomes zero and the instant scr regains forward blocking capability.

-> turn off time is divided into two intowals; vieverly energy time tous and the gate viecovery time tous.

(e.) the toroit the

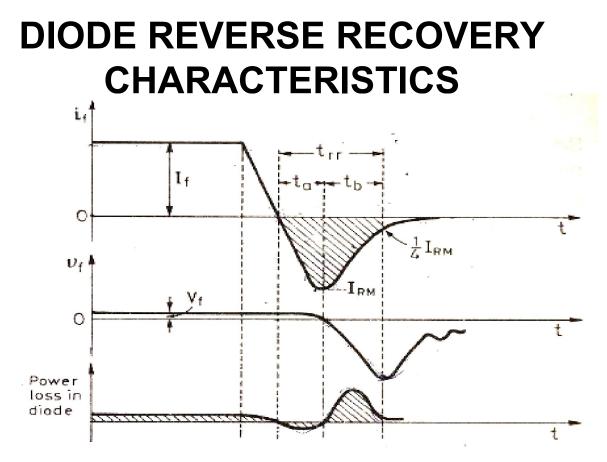

At instant til ande current becomes zero. > After til anode current builds up in the viewse direction with same dildt slope as before to because of the presence

→ The viewerse viecovery current vernoves excers carriers from J1833 between the instants tielts

-> Revence necovery current flows due to the subserving out of holes forom topp-layer to and electrons from bottom n-layer.

The tay when about 60% of the stored charges are remained forom the outer two layers, carrier density across J, El Js begins to decrease and reverse recovery current also starts decaying

→ It decays fast in beginning but gradual thereater. → The fast decay of recovery current causes a reverse voltage a current the device due to the circuit inductance → This sevence nottage Sunge appears across The thypistor terminals of may therefore damage it. → At to when serverse stecovery avoient fails rearly Bero, Ji 833 recover 8 Sce is able to block the sevence hollage.

## witz -05

-> At end of neverse viecovery period (t3-t-), the middle Junction 32 still has heapped block the forward voltage as t3.

-> The changes must decay only by recombination. -> Recombination is possible If a neverse rollage is maintained across SCRI

-> The time for recombination is possible it a se. of changes between to \$ the is called gate recovery time top.

> At try, J2 vecovers of the forward voltage can be reapplied between ande and cathode

>> top (turn-off time) is in range of 3 to loo us.

> ty is influenced by magnitude of forward current, di at the time of commutations and junction temperature dif at the time incoreases with incorease in above 3 factors.

-> If forward current is high before commutation, Imapped changes around Junction 32 are more. -> the fime required for their recombination is more and therefore furn off time is increased.

> The two off-time decreases with an increase in the magnitude of revorse hultage because, it sucks out the courses out of 31 & 33.

> the hum-off time provided to the transistors by the practical circuits is called <u>circuit</u> hum-off time to: -> to is defined as time between the instantanode current becomes zero and the instant neverse voltage due to practical circuit reaches zero.

to > by for reliable two-off. otherwoise the device may two-on at an undesired intant, a process called commutation failure.

-> Thyoustons with slow two-off time (50-100 used) are Called convertor goode sche of too with fast two-off time (3-50 us) are called invertor grade scie.

henogenal with the set to a construction of a with both the the

an pollate the spinor of 210 (and the such ) pl

sign of nothernelmouser which not hereinger and altion

and an account on their salastants with the mal dit a

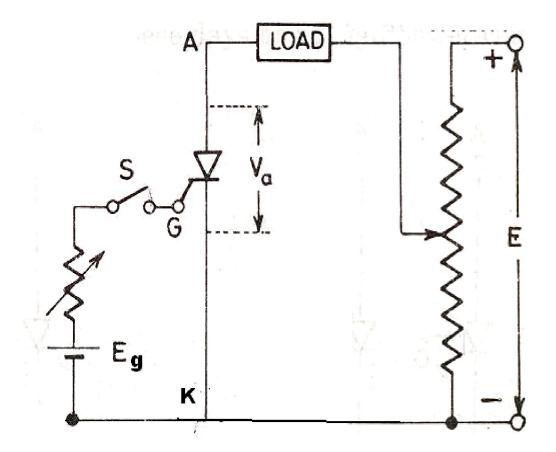

Grate toriggeoring methods

-> Guate triggering is most common method to two-on the sa because this method lends itself accurately for turning on the scr at the desired instant of time.

-> It is an efficient & well able method.

- → By means of gate voltage control, the twining on of the sue can be controlled.

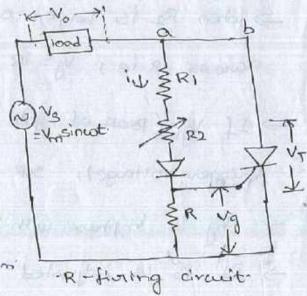

- -> The gate circuit is also called firing or triggering draw (1) Resistance floring circuit:--> It is simple q most economical > Limited mange of fiving angle control (à to 98)) greated dependence on temperature & difference in performance between individual scas are draubbacks which they say

-> R2 is variable mesistance. >If R2 is Beno, gate convert may flow from source, through Was load, RID and gate to cathode.

-> This convent should not exceed maximum permissible gate current Ign

V\_mmaximum values

RI can be found forom

Ign Sousierpitage  $\frac{V_{m}}{R_{l}} \neq I_{gm} \Rightarrow R_{l} \geq$

the gate convert to a the function of R1 is tollmit safe value as R2 is varied

≥ R should have such a value that maximum valage drop across it does not exceed maximum permissible gate voltage Vgm This can happen only when R2 is zero.

under this condition:  $\frac{V_{m}}{R_{1}+R} \cdot R \leq V_{gm}$  $R \leq \frac{V_{gm}R_{1}}{V_{m}-V_{gm}}$

→ As mesistances R, & R2 and lange, gate trigger circuit drows small current

Diode Davous flow of amount during positive half Cycle only. 1e., Ng is half-wave do poulso. The ampli-- tude of this do puse can be controlled by varyings > Potentionneter setting R2 determines the gate voltage amplitude.

Justen R2 is longe, aurent i is small and the rottage across Rie, Vg=iR is also small.

⇒ If Vgp (Reak of gate voltage Vg) is kess than Vgt (gate torigger voltage), sok will not two on. (i.e., Vgp LVgt doesnot transpect with Vs.

⇒ If R2 is adjusted such that Vgp= Vgt, gives x=90° fring angle

⇒ If Vgp>Vgt, as soon as Vg becomes equal to Vgt for first time scr two on a gate loses control and Vg is ineduced to get (almost seve about 1V).

⇒ The fring angle neverbe equal to dever but nearer 1°-4°.

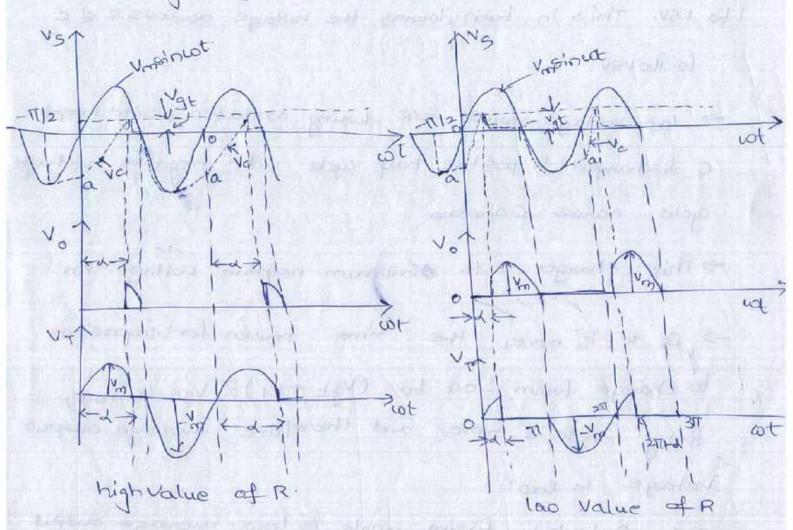

Refining chant .-

> By buying the value of R, fining K-Vot angle can be controlled forom N3 O R2 402 0° to 180°. > T

→ In the negative half cycle, Capacitor C changes through D2 with lower plate positive to the peak supply voltage Vm al which = -9°. Afr

-> After wt=-98, source voltage Vs decoreases forom -Vmat wt=-90° to zero at wt=0°

-Vm at cot=-98 to some lower value - on at cot=0°.

> As sex anode voltage parses through Jeve and becomes positive, C begins to charge through R forom the initial voltage - oa at wt=0

-> When capacitor changes to positive voltage equal to gate torigger voltage Vgt, SCR is fired and after this, corpacitor holds to a small positive voltage. -> Diode Q is used to prevent the breakdown of cathode to gate junction through P2 during regarine half cycle.

WIF-I @

> the firing angle can never be zero \$180°.

SOR will brigger when  $k = V_{QL} + V_d$ where  $V_d$  is the voltage dowop across diode DI''At instant of toriggering) if  $V_c$  is assumed constant, the arrient  $I_{QL}$  must be supplied by voltage source through R, DI & gate to cathode circuit. max.value of R,  $V_s \ge R I_{QL} + V_c$ is given by  $V_s \ge R I_{QL} + V_{QL} + V_d$

- when see triggers, Voltage alop across it falls to I to 150. This in two, lowers the holtage across red c to ito 150.

> 1000 voltage across scr during conduction period keeps C discharged in positive half cycle until negative voltage cycle across Campeans

> This changes C to maximum negative voltage - Vm > If R is more, the time taken for capacitor, to change from - on to (Vgt tVd)? Vst is more, firsting angle is more and therefore average output withage is low. > 24 R is less fivring angle is low, average output voltage is more

$e^{V-1}e^{V-2V} \Rightarrow \mathcal{A}$

I'd retrig in 20

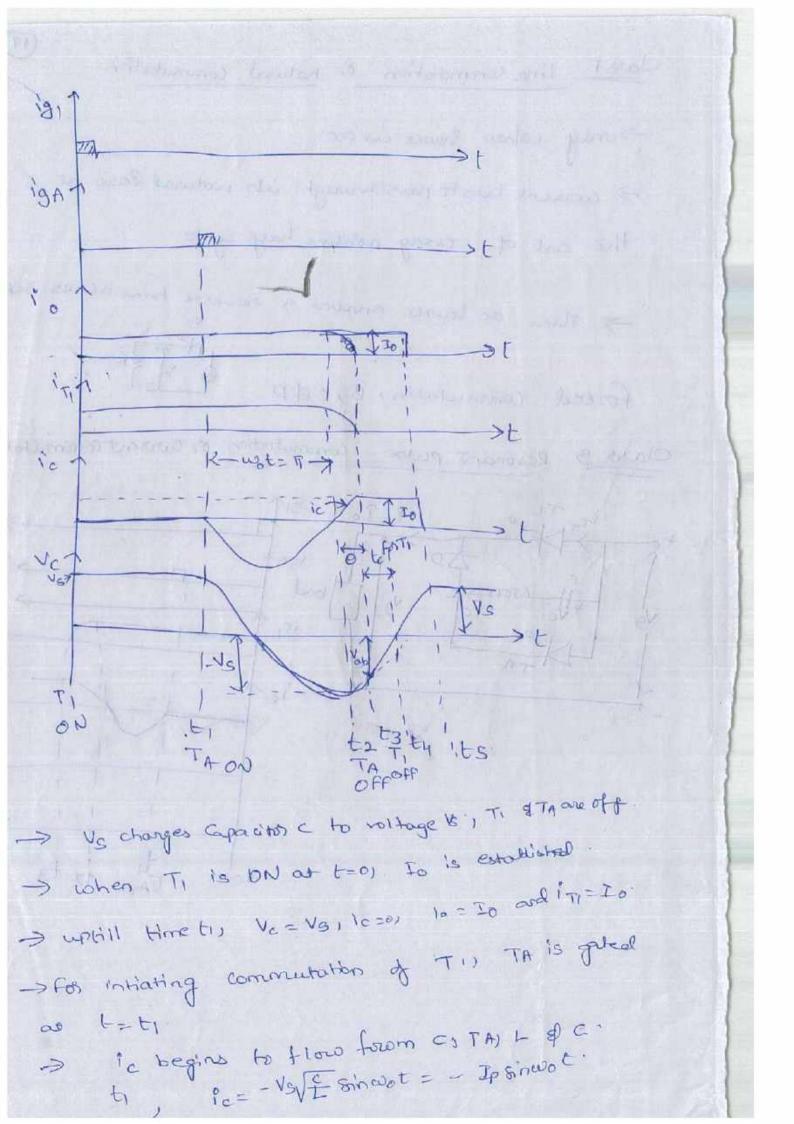

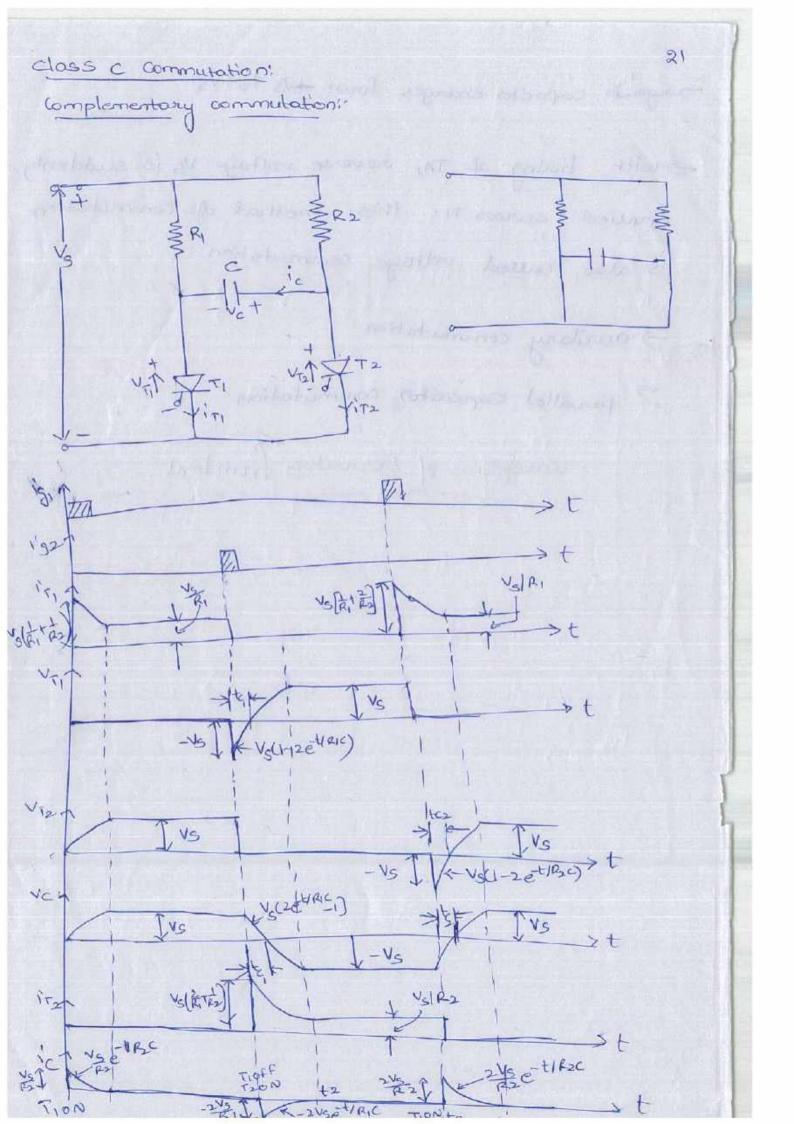

19 Clars F Line commitation & natural commitation. ->only when bounce is ac. -> worrent has to parsthrough its natural ferro at the end of every nositive have cycle -> Then ac bource annues a reverse bias actuals scr At it is R forced commutation, B, CEPP Resonant puble commutation of current commutation Class 1917 9-20 ISAroon > bool iti F & guillow at 2 margare TION TAON to to al all the second cover at all such little the

amerate at enjoy at at at

-> again capacitos charges forom +Vs to+Vs

Swith Histing of TA, oreverse voltage Vs is suddenly annued accross TI. this method of commutation is also called voltage commutation.

-> auxiliary commutation

7 parallel capacitor commutation.

courtering of Dormations from dent

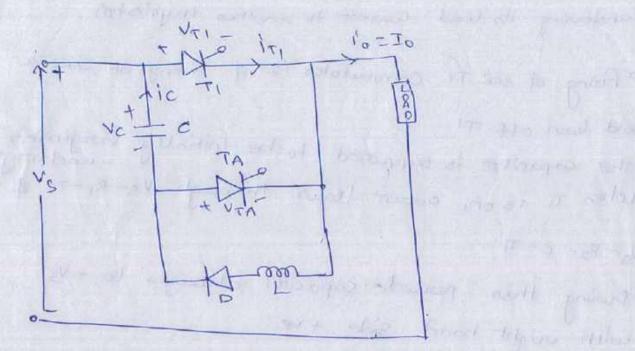

## class D Commutation: of Impulse Commutation

-> Intially TI & Thrane off -> capacitor is assumed to charged to voltage 's with upper plate the

> where  $l_{c=} V_{S} \sqrt{E} Sinvot = 2pointot.$

-> The capacitor discharges from +Vs to Vs. of lower plate becomes +ve > when TA is turned on capacitor voltage Vs applies a revenue voltage accross main thyouiston TI so that VII = - VS & TI is twined OFF.

22

> A thyristor carrying load current is commutated by transferring its load current to another trybistos > Fixing of see TI Commutates T2 of fitting of SER T2 would two off TI -> The capacitor is supposed to be initially virginie; unchanged. -> when Ti is on, ament flows through VS-R1-71 & N5- R2- C- Ti. -> During this period capacitor changes to + Vs with night hand side the -> To commutate the main tryvistor, To is twined the copacitor voltage Vc applies on ' -> At this instant, a nevere witage Vs across scr TI and twens it off the manual states in mature I The copacitor discharges through RI-C-T2 the copacitor voltage changes forom Vs to -Vs

I write I - low is The standar

Jerivation part in Pistoinbre tent

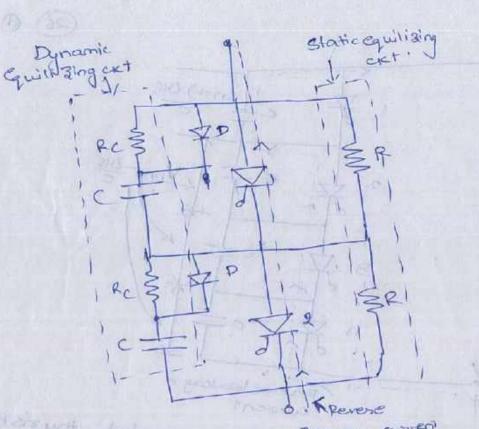

2 0 voltage services operation of scr -> when system voltage is more thank using of a single thysiston, scas one connected in series in string -> sees should have their I-V characteristics as close as possible > on account of inherent variations in their characturistics the voltage shared by each see may not be equal La SCRI leakage veristance = V/ 15 high whereas top see , it is low (Valia) 10802 Po a a latornos de Stong Actual voltage avoient moting of the idide stains Storing -[Endividual voltage avvient rating] [number of scession efficiency the string - one scp Derating factor DRF=1-stong efficiency records altres 200 N1+V2 .1 string efficiency = > The two sces can support a max voltage of VitV2 and not the saled blocking rottage 2V1 > A whitem voltage distribution in steady state Can be achieved by connecting a suitable mesistance

acouss each SCR such that each parallel combination has the same resistance.

-> this will require different value of Relistance for each see which is a difficult proposition.

→ A more practical way of obtaining a nearonably withorm voltage distribution during steady state woulding of series- connected scrs is to connect the Same value of shurt nexistance R across each scr. > This shurt resistance R is called the static equalizing circuit.

-> consider 'n' thypistois connected in series -> Let scal has minimum leakage connent Ibmirand each of the remaining (n-i) sees have some leakage correct Ibmir>Ibmi

->scres with lower leakage awrent blocks more Voltage

> As seel has lover leakage aurrent, it will block voltage Vom(say) which is more than that shared by each of the other (n-1) SCRS. Hore Vom is maximum permissible blocking voltage of Seel.

-> scrs do not have identical dynamic characteristics. -> In such a case, series connected scrs will have unequal Voltage distribution during the transient conditions of two-on two-off

> The dynamic characteristics of two sees during two-on are shown where it is assumed that two-on time of sere is more than that of ser ]

by std stange total tota

unequal voltage distribution of two services connected to sees during (a) two-on and uptwo-off

> Fig both series one gated, string voltage Vs

is shared as vala by each thyristor. at the some hime, As scel has less two-on time, It gets two-on at instant ti , whereas see 2 is yet aff

$\rightarrow$  voltage across SCRI drops from  $V_2$  to almost deta  $\rightarrow$  At the voltage across off SCR2 will boost from  $V_2$  to Vs.

246

-> Thus voltage shared by two scas are unequal -> After to, voltage & across scar may bound on in case & is greater than its breakover holtage -> scar will get two ed on at time (to table).

>During two-off, scrips assumed to have less two-off time by, than that of scrip inity / 1922 > At instant tz, scrips recovered and is passing through zero voltage whereas scrips is developing

-> At tippiboth sees are developing different verence necevery voltages given by ab for seel & ac for sees. -> so two sees have unequal voltages across them at to -> so two sees have unequal voltages across them at to -> Thus it is seen that sees with different charac--toristics during two-off three suffer from unequal voltage distribution during their two-off process.

of two-oft process

-> A simple sesistor for static voltage equalization cannot maintain equal voltage distribution under transient condition. > During transon of two-oild, the capacitance of neveral biased junctions detormines the nothage distribution across sores in a series connected string.

> As verse blaced jurctions are likely to have different capacitances called self capacitances, the voltage distribution during two-on of two-off periods would be wrequal.

> Voltage equilization under these conditions can be achieved by employing shurt capacitors > This agacitance has the effect of removing the inequalities in thysists' self capacitances.

> In otherwords, dwilling twomon and thom-off periods, the resultant of shurt corpacitance & self Carpacitance of each screwterd to be equal for each of the series connected scres

The choice of Capacitor c is based on the servery chonoctantics of server

-> consider 2 scrs connected in series Tat tc a) flow of R. Rewvent current= DE (D) variation of revenue recovery

(25)0 -> SCRI is assumed to have short revenue recovery time as compared to scr2 -> 00 × 41. St is difference in orderse recovery charges of two SCRSI & 2 -> under this assumption seel recovers first; it there fore goes into blocking state & doesnot allow Parcage of excess change 00 left on sce2. -> This OO, pours through c as shown in fig. > voltage induced by DOS in c, accross scel is <u>Do</u> tohere as no voltage is induced by 008 (= 02-01) in C connected a corross Sch2.  $\rightarrow$ : differences in voltages, equal to  $0_2 - 0_1 = 0_2$  to which the two shunt Capacitors are changed -> Sari with least recovery time will share highest transient voltage Vbm -> Transient voltage shared by Slow sce2 must be VEM-00 (less than bon shared by fast scri) : Voltage across scr.W= Vbm 11 11 SCR 2, V2- VENT 00 ·· string voltage = Vev, + V2 = Vbm + Vpm \_ 20= 2Vbm - 20

=> VS=2Vbr 20 > Vbm=1(VS+20) and V2- Vbm-20 = 1[VS-00] the shing tollage sevenes inpolarity in order to aid the R'R process of series in string > NOW Consider for n-series-connected scles in a string if top scel too characteristics similar to scel & remaining cn-1) sces have characteristics similar to scel & remaining scel would recover first & support voltage Vbm: > The charge (n-1)203 from (n-1) sces would pass through 'c'connected aaross top scel & as result, a voltage > (n-1) 008 could be induced in c

exces is 08.

:. voltage across each one of slow thy ristors is  $\left[ \lim_{t \to \infty} \frac{-Dq}{c} \right]$ Thus for a connected sers,

voltage across fout top scel, VI = Vbm

| (1-1) | 31000  | thysistow | $= 1.13V_{2}$ |           |

|-------|--------|-----------|---------------|-----------|

| 25 65 | orta . | policy    | = (n-1) [v_m- | 1 Acres 1 |

20

is string voltage Ve= V, +(n-DV2 Vbm+(n-D)[Vbm-<u>og</u>] Vbm= th [Ve+(<u>n-D)og</u>] C= (<u>n-D)og</u> Nbm-Vs voltage across Each one of slow scess in terms of

11 11

$V_s$  is  $V_2 = \left[V_{Dm} - \Delta \alpha\right] = \frac{V_s}{n} + \frac{(n-1)\Delta \alpha}{nc} - \frac{\Delta \alpha}{c}$  $V_{2} = V_{3} - \underbrace{08}_{C} + \underbrace{000}_{C} + \underbrace$

(26) 0 6-1)003 5 Perene lookage cument connected thyristow Shing having n-series > During two-off, Vs (source nitage) must rere to aid the neverse recovery current. -> The bransient voltage which each see must be able to withstard is Vom -> The total voltage acting across cet consisting of VS, SCRS h, 3, 2, & topc & pen KUL IS VS+ (n-1) DUS & this must be supported by all scas which is equal to n. Vom. : nVpm = Vst (n-1).00 > Vom= + [Vs+ (1-1).0g] => C= CA-1)20 hVpm-Vs

Reavery aurent Stoken any acel is F.B. state, capacitor connected access it gets change to volhage existing across see that acc. s when this ace is twined on, c discharges heavy awvent twough this ace. For limiting this current spike, a damping mesistor Re is used in series with c. Re also dompsout high frequency additations that may arise due to keyshunt Capacitor d ext inductance.

> combination of RC & C is called dynamic equilising circuit. > RC & C used is to equalise the nothage during dynamic (or transient) conclitions \$ to protect sces against high dyldt

-> when forward voltage appears, diode D by passes Rc during changing time of Capacitos G, makes copacitos more effective in voltage equalization of for limiting du across see. -> During Capacitor discharge Rc corres into play for limiting current spike of dildt.

T (84) Thyou's to protection. ->Policeliable operation of a thysistor, its specified matings must not exceed: -> In practice, a thuriston may be subjected to overvoltage and over awrents. The below of the post ways which of -> During scR twon-on, di may be very large > There may be false truggeoing of scr by high value of du -> A spurious signal across gate athode teaminals may lead to unwanted two-on. -> scrs are very delicate devices, their protection against

abramal operating conditions is, therefore, exertial.

- neighbourhood of the first the whole area of junction. -)trightrouvernt sporeads across the whole area of junction. ->2p the roote of visce of anode current, i.e., dit is longe as compared to the spread velocity of corriers, local hat sports will be formed near the gate connection on account of high averent density. This localised heating may destroy the thyritty.

- i. di at the time of two-on must be kept below the specified limiting value.

- -> di can be maintained below acceptable limit by using a small inductor, called di inductor, inservices with anode circuit.

→ Typical didt limit values at scrs are 20-500 Aluse. (b) dv/dt protection: NO.K.T if mate of ourse of suddenly applied voltage accross thyouston is high, the device may get twened on. dv twomon must be avoided as it leads to false operation of thyouston circuit.

→ dv bit course of vuise of forward anode to cathods noting dvaldt must be kept below specified viated limit. Typical values of dubit are 20-500 v1 usec: > False two-on by, dvldt Can be prevented by using a Snubber circuitin parcolled with the device

Design of Snubber circuit: > A snubber circuit censible of a services combination of mesistance Rs and capacitorie Ce In parallel with thrymistor: -> Capacitor G in parallel with device is sufficient to

prevent unwanted duldt truggering of sor.

-> when switch S is closed, a sudden voltage appears across drawit. Cs behaves like a short drawit, therefore across Cs builds up at a slow onate such that duld t awoss Cs & therefore across scr is less than specified maximum duldt mating of the device. -> Before scr is fired by gate pulse, Cs changes to

fue voltage Vs. when scr is twend on , capacitor

Capacitos discharges through the site of sends a current equal to VSI Consistance of local path formed by Cs and SCR). > As this oresistance 18 quite loco, the tuan-on dildt will tend to be excersive and as a vesult, sce may be destroye > Inorder to limit the magnitude of discharge current a resistance Rs is inserted in series with cs of turnon dildt is weduced:

> Rs, is & load circuit parameters should be such that dolds across a during its charging is less than the Specified duldt rating of the SCR of discharge avoient al the two-on of scr is within seasonable limit -> Normally, RS, Cs & load circuit parameters form an underdamped circuit so that duldt is limited to acceptable values. Shubberch Shubberch Ressing Ressi SCR in series with R. Thysistor protection with equation instants is (a) L&RSISS (b) (c) with (all a car and a view) and in -> when s is closed, G behaves like a short cut and ecr In the forward blocking state offers a high revision ce The forward block of the fig (c): ther eq ext is shown in fig (c): for ext (C),  $V_{S} = (R_{S} + R_{L})i + L\frac{di}{dt}$   $\rightarrow i = I(I - e^{-t/T}), I - \frac{V_{S}}{R_{S} + R_{L}} \neq T = \frac{L}{R_{S} + R_{L}}$   $\frac{di}{dt} = \frac{d}{dt} (I(I - e^{t/T})) = I \cdot e^{t/T} \cdot \frac{L}{T} = \frac{V_{S}}{R_{S} + R_{L}} \cdot \frac{R_{S} + R_{L}}{L - e^{t/T}}$ = Vs -t/ 2

Value of dildt is maximum when t=0.

$$\begin{pmatrix} \frac{di}{dt} \\ \frac{dt}{dt} \\ \frac$$

Voltage across SCR, Va = Rg. 1

How Hell Les 1987

ant ment

British

I anotalena suit M

52 Blanson 46/16

to patter this bolt and

$$\begin{bmatrix} dVa \\ dt \end{bmatrix} max = \frac{R_sV_s}{r_s}$$

Imar

L. MAST ( ( SAT) L =

reduced So

-> over convent purotection -> over voltage purotection >dildt protection -> dv/dt purotection

-> brate protection sagainst onervoltages & overcurrents which causes faise touggering of see & damages -> Zenone Zener diode is connected acrurs gate crt -> Resistor connected in series with gate extprovides tratection against over aurents.

22

→ noise can meduced by shielded cables -> Resistor & Capacitor are also connected acruss gate to cathode to by pass noise signals. > c must be less than o'luf of must not detrionate wave shape of gate public

Thysuistor psudection circuit components Snubber circuit overcountert protection di inductor C'B FACLE ARS Supply Grate protection Heatink Transto 1 03 2'D A RIACITI FACLF > Fost acting current limiting tw C'B > circuit Breaken, Z.D -> Zenen diode

(5) -> chen connect punchection anitastand spictor ravise THILS picchetten addations about a pietes descentarios à espetitives renicopose noticataing stade. Anone source is converted and grant Realiston connected in sevires with gave and proces production appind over animate noise convisions by shielded coules soon telasmos our ana ratengo te concest shorp's solan avoid of shitting of the four burn a full of white and sol tought a ct allowing productions and shared making the Harver and Annes DEN A the screenst present in a lost whether the start the second of

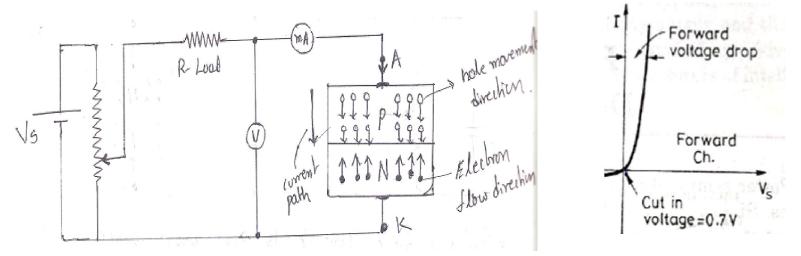

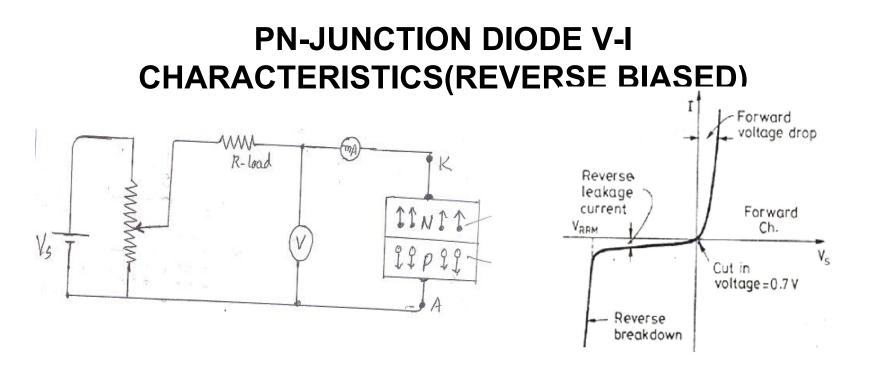

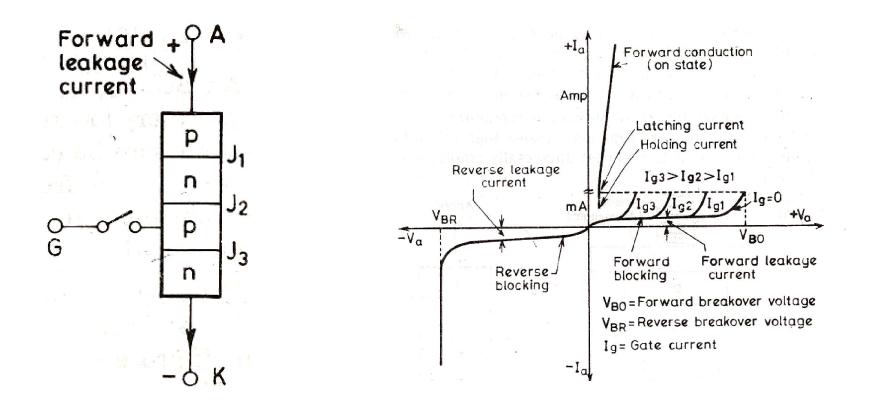

STATIC IV characteristics of a thyoustos:

> When During Followed bias Jig J3 -> forward based

J2 -> Reverse blased

> Reserve of depletion layer at J2, does not allow any current to frow through the device

-> only leakage current, negligibly small in magnitude, flow through the device due to the don't of the mobile charges this current is insufficient to make The

-> The depletton layer, mostly of immobile changes do not Constitute any-flow of current

> This is forward blocking state or off state of the + -> The width of the depletion layer at the jurction J2 decreases with the increase in anode to cathod Woltage (Since - The width is inversely proportional to voltage)

> If the voltage blue and of cathode thereases its tept on increasing, a brage comes (corresponding to forward break over voltage) when the depletion layer at J2 Vanishes -> The onevenue blased junction J2 will breakdown due to

The large voltage gradient aaross its depiction layer This phenomenon is known as the Avalanche Breakdow -> since J1 & J3 are already forward blased, there will be a free Gassier movement across

all the three junctions mesulting in a large amount of council flowing from anode to calhode. > Due to the flow of this forward courset, The device starts conducting El It is then said to re In torressed conducting state or on state.

> when Cathode is made positive corr. to end p byer, J2 becomes Eb, J1 & J3 becomes R'B -> J1 9 32 do not allow any worrent totlaw through ->only a very small amount of leatage current may device. flow because of the doubt of the changes -> The leakage currere is unsufficient to make the

device conduct.

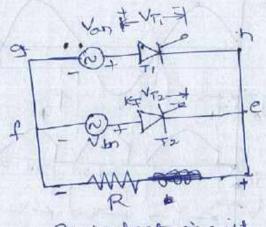

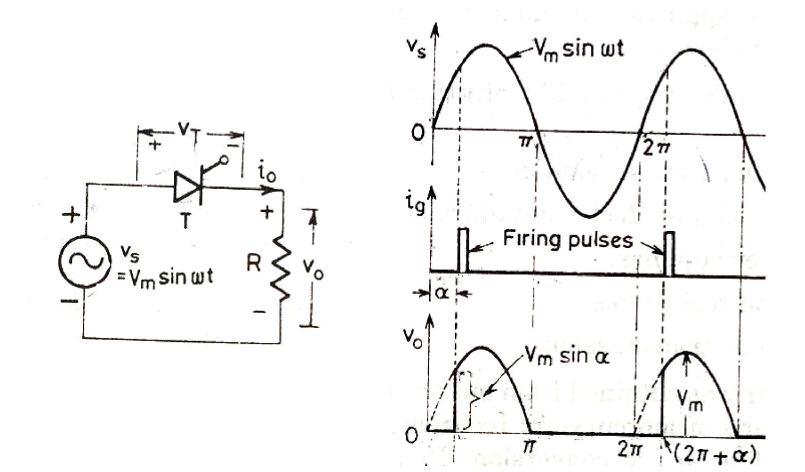

Converters